I’ll start this post with a small apology.

It’s the dog days of summer. Everyone’s thinking vacation. Or back to school. Or cooling off. Or all three. So this is something of a heavy duty topic to ask you to read up on. But just a few days ago, I came across a three-part article on embedded.com, in with Reuven Dobkin addressed the topic of “Asynchronous reset synchronization and distribution – challenges and solutions.”

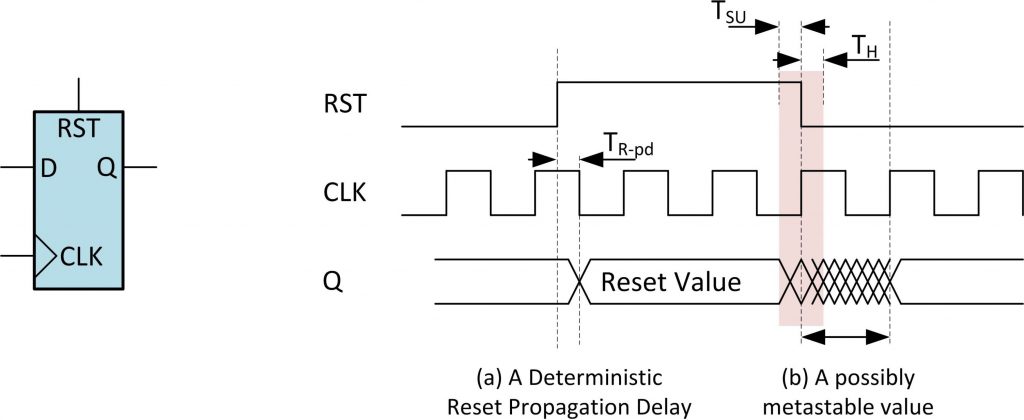

These types of resets are used in VLSI designs to ensure that synchronous circuitry is brought to a known state after power up. To do this, the reset operation needs to be coordinated with the logic clock signal to that there are no contention issues between the reset and the clock.

Why tackle this subject? As Reuven explains:

Lack of coordination between asynchronous resets and synchronous logic clocks leads to intermittent failures on power up.

In his series, Reuven shares his insights and provides some valuable guidance:

The drawbacks of classic solutions for reset synchronization (reset tree source synchronization) and distribution (reset tree synthesis) are discussed. Advanced solutions for faster and simpler timing convergence and more reliable reset synchronization and distribution are presented. Different approaches for ASIC versus FPGA designs are detailed.

In Part 1 of his series, Reuven details the drawbacks that asynch reset present, including metastability in flip-flops. Whatever the drawbacks, asynch resets are widely used, so it’s important that engineers fully understand what’s going on with them. (There are a number of pros and cons to both asynch and synchronous resets, and the decision on which method to deploy will depend on the situation, but the article doesn’t delve in too deeply there.) The opening article in the series outlines some solutions. In Part 2, he goes further, focusing on making sure that asynch reset is done correctly for ASIC and FPGA. solutions for correct asynchronous reset in ASIC and FPGA. In Part 3, Reuven tackles some special cases to the reset synchronization and distribution problem.

I know, I know. It’s mid-August, and sometimes it’s hard to wrap your mind around material like this. So you might want to bookmark it, and pick it up again in a few weeks when school’s back in session!