Document: MitySOM-AM57F Carrier Board Design Guide

Revision: 1.2

Date: November 6, 2024

### 1 Overview

### 1.1 MitySOM-AM57F Fast Facts for Getting Started

| Facts                                                                   | MitySOM-AM5728F, MitySOM-AM5748F, MitySOM-AM5749F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Required connectors                                                     | JAE MM70-314B1-2-R300: card edge receptacle                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| placed on carrier board                                                 | HiRose DF40HC(3.0)-100DS-0.4V(58) : fine-pitch hi-speed header                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Input Voltages supplied                                                 | +5V (to SOM on-board power supply / power management IC),                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| from carrier board                                                      | +1.8 to +3.3V (FPGA bank I/O)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Supported I/O standards                                                 | LVTTL, LVCMOS33, LVCMOS25*, LVDS25*, LVCMOS18*                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Total number of FPGA I/O's                                              | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Number of LVDS capable I/O's                                            | 48 pairs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SOC Cores, speeds                                                       | • 2x ARM Cortex-A15 @ 1500 MHz max.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                         | <ul> <li>2x 66x floating point DSP cores @ 750 MHz max.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                                                                         | <ul> <li>2x ARM Cortex-M4 Image Processing Unit (IPU) @ 212.8 MHz max.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SOC Peripherals**                                                       | <ul> <li><u>Video Processing:</u></li> <li>LCD Display / HDMI support, Image Video Accelerator (IVA)</li> <li>3D Graphics Processing Unit (GPU), Video Processing Engine (VPE)</li> <li>Embedded Video Engine (EVE): AM5749 only</li> <li><u>Program / Data Storage:</u></li> <li>2.5 MB on-chip shared RAM</li> <li>General purpose memory controller (GPMC)</li> <li>Dual DDR3 memory controller, dynamic memory manager (DMM)</li> <li><u>Interface Support:</u></li> <li>Dual Controller Area Network (CAN)</li> <li>Dual Ethernet (MII, RMII or RGMII interface support)</li> <li>Up to 199x SOC General Purpose I/O (GPIO)</li> <li>Up to 5x I2C, up to 8x Multichannel Audio Serial Port (McASP)</li> <li>Multi Media Card, Secure Digital I/O (MMC, SD, SDIO): up to 4x</li> <li>PCI Express 3.0, Serial Advanced Technology Attachment (SATA)</li> <li>up to 4x Multi-channel Serial Peripheral Interface (McSPI)</li> <li>Quad Serial Peripheral Interface (QSPI)</li> <li>up to 10x Universal Asynchronous Receiver/Transmitter (UART)</li> <li>USB 3.0 with SuperSpeed, dual role device support</li> <li>USB 2.0: with high speed, dual role device support</li> </ul> |

| *Requires external bank voltage su<br>**Peripherals share pins, see AM5 | • USB 2.0: with high speed, dual role device support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Page 1 of 47

Document Revision: 1.2 – MitySOM-AM57F CBDG

Critical Link reserves the right to make corrections, modifications, enhancements, and other changes to this document at any time and without notice.

### 1.2 Introduction

The MitySOM-AM5728F, MitySOM-AM5748F and MitySOM-AM5749F modules (collectively referred to as MitySOM-AM57F) are System-On-Modules (SOMs) designed to be easy to integrate into an end-user embedded system. The modules integrate many crucial elements of an embedded system and do so with an established design framework utilizing a common set of core libraries. End-user design of the application PCB is also intended to be as simple as possible, allowing the PCB designer to concentrate on the custom I/O interfaces – especially analog & mixed-signal – instead of getting distracted with the learning curve of designing a brand new embedded digital system from scratch.

Developers are encouraged to review the MitySOM-AM57x Development Kit design schematics, available on the Critical Link support site. The Development Kit has been qualified with a full software support package available for the interfaces and devices on the board. Customers may contact Critical Link for access to Altium CAD design files for the development kit and for design reviews, email <a href="mailto:support@criticallink.com">support@criticallink.com</a>

A schematic design checklist is available from the Critical Link support Wiki for customer carrier boards designed around AM57x SOM series. The checklist is a baseline for Critical Link reviews of customer designs. Please see "Reference Documents and Links" section of this document for a link.

### 1.3 MitySOM-AM57F Family Modules

The MitySOM-AM57F family of modules represents a 5<sup>th</sup> generation SOM in the MityDSP/MitySOM product line. These modules are based on Texas Instruments AM57x System-On-Chip (SOC) Sitara processors. Each of these SOC devices are footprint-compatible devices using a 760-PBGA package with summary features described in section 1.1 (Fast Facts) above.

Each MitySOM-AM57F SOM includes a power supply & management subsystem, DDR3 SDRAM, NOR FLASH memory, and interfaces to a carrier board with a 314-pin low-profile MXM card-edge receptable and a 100-position, fine-pitch, low-profile connector set. AM57F SOMs also integrate a Xilinx/AMD Artix-7 FPGA for end-user customizable logic and I/O interfaces beyond the capability of the SOC device. Carrier board design for the "F" type of MitySOM (with FPGA) is the main focus of this document.

MitySOM-AM57F products are available with options for AM57x SOC device variant, RAM and FLASH memory depth, FPGA size and operating temperature range. Please visit the "MITYSOM-AM57F" product page or contact Critical Link for the current list of orderable MitySOM-AM57x part numbers.

### 1.4 MitySOM-AM57 Family Modules (No FPGA)

Available alternates to the MitySOM-AM57F family have no Artix-7 FPGA installed. This "AM57" (no "F") SOM type is less expensive and requires less power than a comparable AM57F SOM with FPGA. IO pins reserved for the FPGA on the AM57F SOM are routed to additional peripheral interfaces on the SOC processor. See separate SOM datasheets and carrier board design guide for the MitySOM-AM57 module types.

#### 1.5 SOM Dimensions

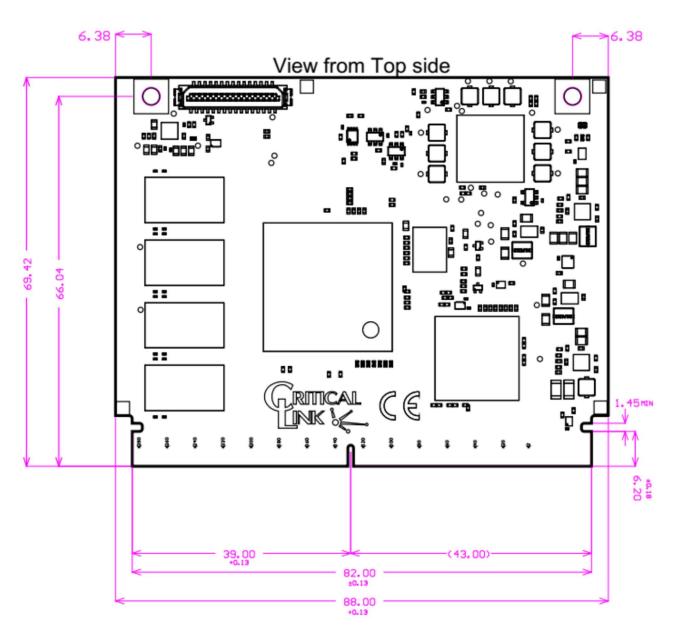

The dimensions of the MitySOM-AM57F are 88.00mm (~3.46in) x 69.42mm (~2.73in) and features two mounting holes at the end of the SOM where the 100-pin connector, J3, is located. See Figure 1 for top view.

Figure 1: MitySOM-AM57F Mechanical Drawing

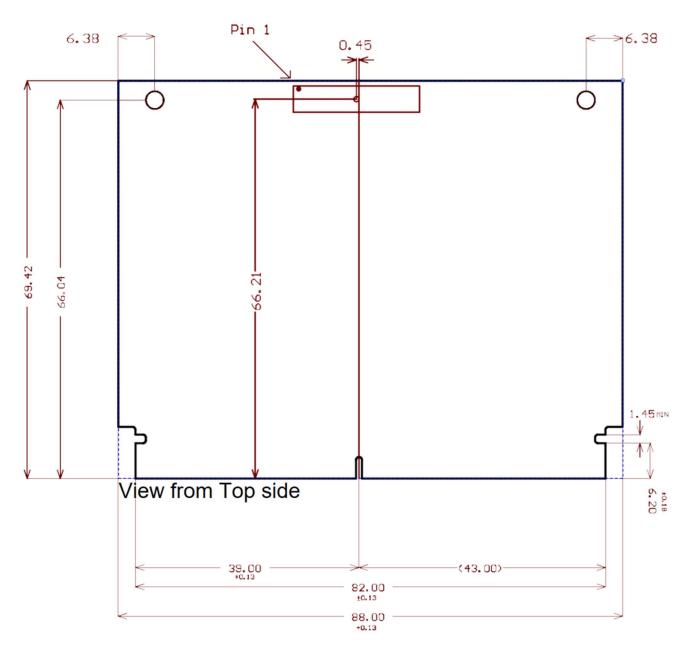

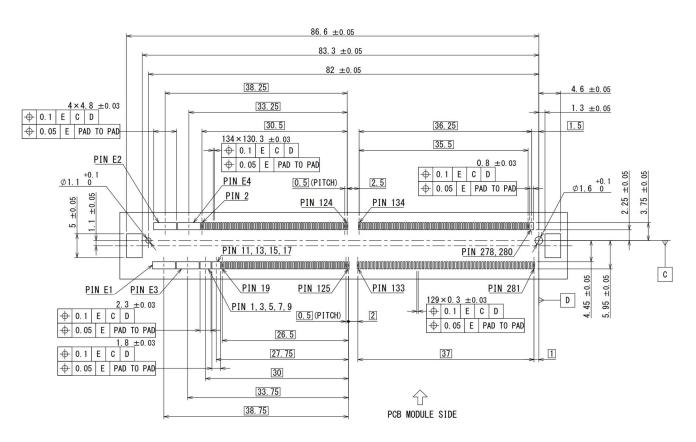

The mechanical outline of the MitySOM-AM57F is illustrated in Figure 2 and shows the location of the bottom side-mounted 100-pin fine-pitch plug-type connector (J3). The center of this 100-pin connector is the reference point for its placement.

Figure 2: MitySOM-AM57F 100-pin bottom side connector location (J3)

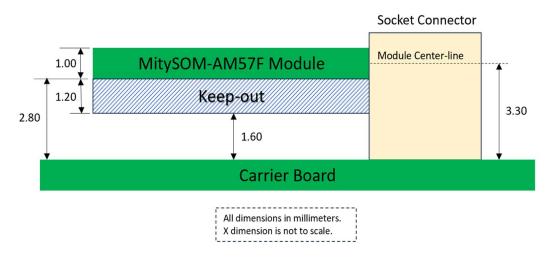

### 1.6 Carrier Board: SOM Outline

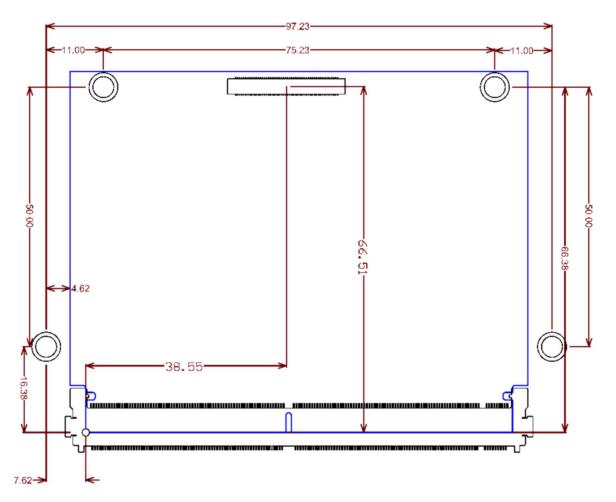

Figure 3 specifies the recommended carrier board outline for placement of the mating 100-position receptacle and mounting holes for fasteners. Dimensions are referenced from the left alignment pin position of the MXM connector; this point is analogous to the SOM lower left inset corner shown in Figure 2. As in Figure 2, the center of the 100-position receptacle connector is the reference point for its placement.

Note that the vertical spacing between the reference (MXM alignment pin) and the center of the 100-position receptacle connector on the carrier board is slightly longer (by 0.3 mm) than the distance from SOM card edge to J3 connector shown in Figure 2. This accounts for tolerances in the MXM connector insertion depth to allow for proper alignment of when mating the 100-position connector set.

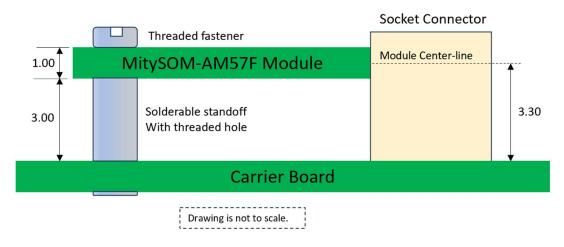

Fastener mounting holes on the carrier board should be sized for installation of 3 mm high threaded spacers or stand-offs. Recommended spacer part number: Penn Engineering SMTSOB-M3-3ET or equivalent. The 3 mm spacer height matches the board-to-board distance between the carrier board and SOM when the SOM is fully seated into the recommended JAE 314-pin MXM card edge connector and the HiRose 100-position connector set.

Page 5 of 47

Figure 3: Recommended MitySOM-AM57F Carrier Card Outline with heat spreader mounting holes

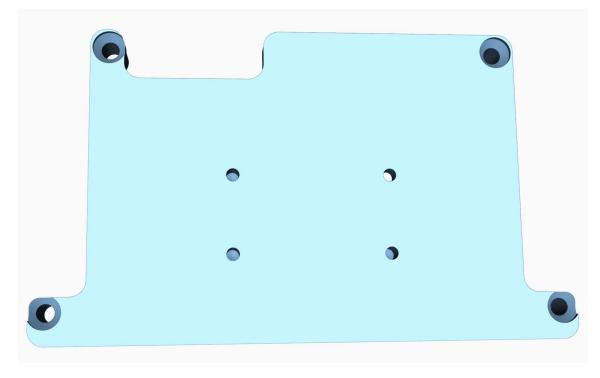

If a heat spreader / heat sink solution is required, Critical Link recommends placing two additional mounting holes outside of the SOM outline area at the end near the MXM connector as shown. See Figures 4 and 5 for top and bottom renderings of Critical Link heat spreader 94-900813-3, designed for use with MitySOM-AM57F. Design files for this heat spreader are available from Critical Link on request.

See Section 5 of this document for additional Carrier Board Mechanical requirements.

Figure 4: Heat Spreader 94-800913-3 Top Side View (faces away from SOM)

Figure 5: Heat Spreader 94-800913-3 Bottom Side View (faces SOM)

Page 7 of 47

### 1.7 Reference Documents and Links

From Critical Link LLC:

MitySOM-AM57F Product Page:

https://www.criticallink.com/wp-content/uploads/MitySOM-AM57F-Data-Sheet.pdf

#### MitySOM-AM57x Support (Wiki):

https://support.criticallink.com/redmine/projects/mitysom\_am57x/wiki

#### MitySOM-AM57F Data Sheet:

https://www.criticallink.com/wp-content/uploads/MitySOM-AM57F-Data-Sheet.pdf

#### MitySOM-AM57(F) Family Development Kit Product Page:

https://www.criticallink.com/product/mitysom-am57f-development-kit/

#### MitySOM-AM57x Carrier Schematic Checklist:

https://www.criticallink.com/wp-content/uploads/MitySOM-AM57x-Carrier-Schematic-Checklist.pdf

#### From Texas Instruments:

AM57x Sitara Processor Data Sheet: TI document: SPRS953 rev. G revised Nov. 2019

https://www.ti.com/lit/gpn/am5728

#### AM57x Sitara Processor Technical Reference Manual:

TI document: SPRUHZ6 rev. L revised Aug. 2019 https://www.ti.com/lit/pdf/spruhz6

#### TPS659039 PMIC Product Page:

https://www.ti.com/product/TPS659039-Q1

From Xilinx/AMD:

Artix 7 FPGA Product Page: <u>https://www.xilinx.com/products/silicon-devices/fpga/artix-7.html</u>

Page 8 of 47

### 2 Connectors

The MitySOM-AM57 utilizes a dual connector set to physically interface with the end user's application board ("SOM Carrier" or "Carrier" board). Recommended sources for carrier board connectors are listed below in bold type.

- 314 position, MXM-style card edge connector provides primary access to SOM I/O:

- SOM board: 'gold finger' pads spaced at 0.5 mm pitch on top and bottom sides along board edge, with pad gap for 'key' notch, no physical connector

- Carrier board card edge receptacle: JAE MM70-314B1-2-R300

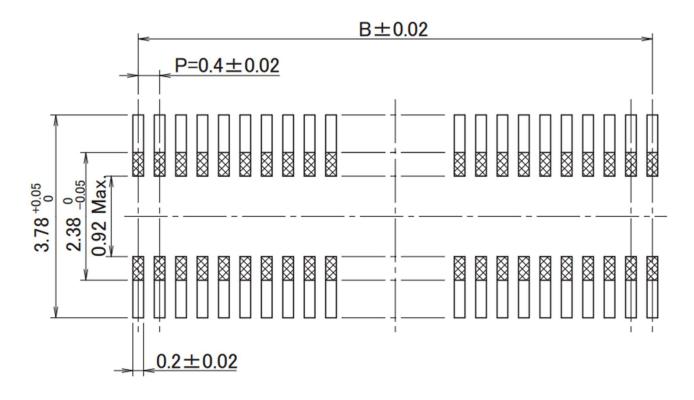

- 100-position (dual row, 50 positions per row), 0.4 mm pitch, 3.0 mm mating height, high speed-capable connector set provides access to additional SOM I/O:

- SOM board plug-type connector: HiRose DF40C-100DP-0.4V(51)

- Carrier board receptacle-type connector: HiRose DF40HC(3.0)-100DS-0.4V(58)

This connector set was chosen for its high density, compact size, ease of procurement, and low cost. With the MXM card edge connector, a physical socket component is only required on the carrier board. The connector set allows the MitySOM-AM57F module to lay flat, parallel to the carrier board surface with a 3.0 mm board-to-board distance. The mounting method is similar to installation of expansion memory and interface cards into compact equipment like laptop computers.

### 2.1 MXM Card-edge Compatibility

The MXM interface, consisting of a set of card edge-placed "gold finger" pads on top and bottom sides of a plugin board, and a mating receptacle connector on a host or carrier board, was developed for PCI Express (PCIe) graphic adapter cards which install onto PC motherboards -- similar to memory expansion cards using an SO-DIMM card edge connector. **Please note that the MitySOM-AM57F is NOT electrically compatible with the PCIe socket standard**, and intermixing modules/sockets from the two standards would very likely cause permanent damage to one or both sides of the interface.

The MitySOM-AM57F shall only be installed into a board which is designed for compatibility with the SOM's pinout and electrical characteristics.

Standard MXM connector footprints have the following characteristics which are not compatible with the MitySOM-AM57F pin-out and must be designed out of a Carrier Board PCB footprint:

Common PCB pad is shared for these pin groups:

- E1[1:9], E2[1:9], E3[2:10], E4[2:10],

- Pins [1, 3, 5, 7, 9]; pins [11, 13, 15, 17]; pins [279, 281]

PCB pads are not provided for these pin positions:

• E1-10, E2-10, E3-1 and E4-1 (from legacy 310-position connector design);

Total PCB pad calculation: 281 numbered pins minus 7 "key" deletions plus 40 E-pins equals 314 pads.

The carrier board footprint for the MXM-style card edge receptacle compatible with the MitySOM-AM57F must provide individual PCB pads for all 314 available connector pins. Developers of carrier board designs may request SOM and MXM connector footprints from Critical Link which are compatible with Altium Designer.

For backward compatibility with legacy 310-pin connectors, Critical Link recommends defining pins E1-10, E2-10, E3-1 and E4-1 as "no connects" in the carrier board design. These pins have no connections on the MitySOM-AM57F module.

#### 2.2 MitySOM-AM57F Pin-out

**Error! Reference source not found.** and 2 contains a summary of the MitySOM-AM57F connector pin mapping which includes:

- Connector pin assignment

- Voltage domains

- B15 and B34 indicate Artix 7 FPGA Bank 15 and 34 voltages; these are sourced from the Carrier board side of MXM card edge connector. Voltage range: +1.8 to +3.3 V.

- FPGA or AM57XX ball location for signals which directly connect with Carrier board

- Signal Types for each pin. <u>Notes</u>:

- 'FPGA' signal types: the signal option name is of the form IO\_<BANK>\_<LVDSPAIR>\_<N/P>

- 'MFIO' (multi-function I/O) signal types: pin multiplexing (PINMUX) utility, sourced from Texas Instruments, must be utilized to configure valid combinations of peripheral devices. Not all combinations are supported. Except for MMC pins (+3.3 V), MFIO signals are +1.8 V logic.

- 'PWR' and 'GND' types are reserved for power and ground

- 'FF' (fixed function) and 'PMIO' (power management I/O) signal types have dedicated SOM functions and shall not be re-assigned. Most signals in these groups have interface-specific voltage characteristics.

- Table 1 (card edge connector): Red shaded rows: reserved for other SOM functions; do not reassign

- Table 2 (100-pin connector set): see legend for colored row restrictions

- 'NC' and 'KEY' pin types have no connection on AM57F SOM.

- Signal Options for each pin: Refer to manufacturer documentation for descriptions of the various peripheral choices, pin functions and valid pin multiplex (PINMUX) settings. This documentation includes:

- AM57x device datasheet

- AM57x Technical Reference Manual

- PINMUX utility

#### Table 1: MitySOM-AM57F Card-edge (J1) Pin-out

| Pin | Туре | FPGA<br>Bank or<br>Voltage<br>Domain | FPGA<br>ball | 57xx<br>ball | Signal<br>Option 1 | Signal<br>Option 2 | Signal<br>Option 3 | Signal<br>Option 4 | Signal<br>Option 5 | Signal<br>Option 6 | Signal<br>Option 7 | Signal<br>Option 8 | Signal<br>Option 9 | Signal<br>Option 10 | Signal<br>Option 11 | Signal<br>Option 12 | Signal<br>Option 13 |

|-----|------|--------------------------------------|--------------|--------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|---------------------|---------------------|---------------------|---------------------|

| 1   | FPGA | B15                                  | B17          | -            | IO_15_L16_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 2   | FPGA | B15                                  | C18          | -            | IO_15_L18_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 3   | FPGA | B15                                  | C16          | -            | IO_15_L16_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 4   | FPGA | B15                                  | D18          | -            | IO_15_L17_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 5   | FPGA | B15                                  | D16          | -            | IO_15_L14_N        |                    | SRCC_N             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 6   | FPGA | B15                                  | E17          | -            | IO_15_L17_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 7   | FPGA | B15                                  | E16          | -            | IO_15_L14_P        |                    | SRCC_P             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 8   | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 9   | FPGA | B15                                  | F15          | -            | IO_15_L21_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 10  | FPGA | B15                                  | E18          | -            | IO_15_L24_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 11  | FPGA | B15                                  | G15          | -            | IO_15_L21_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 12  | FPGA | B15                                  | F17          | -            | IO_15_L24_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 13  | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 14  | FPGA | B15                                  | F18          | -            | IO_15_L19_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 15  | FPGA | B15                                  | G16          | -            | IO_15_L20_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 16  | FPGA | B15                                  | G17          | -            | IO_15_L19_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 17  | FPGA | B15                                  | H16          | -            | IO_15_L20_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 18  | FPGA | B15                                  | H18          | -            | IO_15_L23_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 19  | FPGA | B15                                  | C11          | -            | IO_15_L4_P         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 20  | FPGA | B15                                  | H17          | -            | IO_15_L23_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 21  | FPGA | B15                                  | B11          | -            | IO_15_L4_N         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 22  | FPGA | B15                                  | C8           | -            | IO_15_L1_N         | ADON               |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 23  | FPGA | B15                                  | A13          | -            | IO_15_L8_P         | AD10P              |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 24  | FPGA | B15                                  | D8           | -            | IO_15_L1_P         | AD0P               |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 25  | FPGA | B15                                  | A14          | -            | IO_15_L8_N         | AD10N              |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 26  | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| Pin | Туре | FPGA<br>Bank or<br>Voltage<br>Domain | FPGA<br>ball | 57xx<br>ball | Signal<br>Option 1 | Signal<br>Option 2 | Signal<br>Option 3 | Signal<br>Option 4 | Signal<br>Option 5 | Signal<br>Option 6 | Signal<br>Option 7 | Signal<br>Option 8 | Signal<br>Option 9 | Signal<br>Option 10 | Signal<br>Option 11 | Signal<br>Option 12 | Signal<br>Option 13 |

|-----|------|--------------------------------------|--------------|--------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|---------------------|---------------------|---------------------|---------------------|

| 27  | FPGA | B15                                  | A15          | -            | IO_15_L10_N        | AD11N              |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 28  | FPGA | B15                                  | A12          | -            | IO_15_L7_N         | AD2N               |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 29  | FPGA | B15                                  | B14          | -            | IO_15_L10_P        | AD11P              |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 30  | FPGA | B15                                  | B12          | -            | IO_15_L7_P         | AD2P               |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 31  | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 32  | FPGA | B15                                  | B15          | -            | IO_15_L9_N         | AD3N               |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 33  | FPGA | B15                                  | C13          | -            | IO_15_L11_N        |                    | SRCC_N             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 34  | FPGA | B15                                  | C14          | -            | IO_15_L9_P         | AD3P               |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 35  | FPGA | B15                                  | D13          | -            | IO_15_L11_P        |                    | SRCC_P             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 36  | FPGA | B15                                  | D14          | -            | IO_15_L12_N        |                    | MRCC_N             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 37  | FPGA | B15                                  | C12          | -            | IO_15_L6_N         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 38  | FPGA | B15                                  | E13          | -            | IO_15_L12_P        |                    | MRCC_P             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 39  | FPGA | B15                                  | D11          | -            | IO_15_L6_P         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 40  | FPGA | B15                                  | F14          | -            | IO_15_L22_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 41  | FPGA | B15                                  | C9           | -            | IO_15_L2_N         | AD8N               |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 42  | FPGA | B15                                  | G14          | -            | IO_15_L22_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 43  | FPGA | B15                                  | D9           | -            | IO_15_L2_P         | AD8P               |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 44  | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 45  | FPGA | B15                                  | D15          | -            | IO_15_L13_N        |                    | MRCC_N             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 46  | FPGA | B34                                  | V8           | -            | IO_34_L24_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 47  | FPGA | B15                                  | E15          | -            | IO_15_L13_P        |                    | MRCC_P             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 48  | FPGA | B34                                  | V7           | -            | IO_34_L24_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 49  | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 50  | FPGA | B34                                  | U7           | -            | IO_34_L23_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 51  | FPGA | B34                                  | R3           | -            | IO_34_L14_P        |                    | SRCC_P             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 52  | FPGA | B34                                  | V6           | -            | IO_34_L23_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 53  | FPGA | B34                                  | T2           | -            | IO_34_L14_N        |                    | SRCC_N             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 54  | FPGA | B34                                  | M6           | -            | IO_34_L8_P         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| Pin | Туре | FPGA<br>Bank or<br>Voltage<br>Domain | FPGA<br>ball | 57xx<br>ball | Signal<br>Option 1 | Signal<br>Option 2 | Signal<br>Option 3 | Signal<br>Option 4 | Signal<br>Option 5 | Signal<br>Option 6 | Signal<br>Option 7 | Signal<br>Option 8 | Signal<br>Option 9 | Signal<br>Option 10 | Signal<br>Option 11 | Signal<br>Option 12 | Signal<br>Option 13 |

|-----|------|--------------------------------------|--------------|--------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|---------------------|---------------------|---------------------|---------------------|

| 55  | FPGA | B34                                  | R2           | -            | IO_34_L13_P        |                    | MRCC_P             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 56  | FPGA | B34                                  | N6           | -            | IO_34_L8_N         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 57  | FPGA | B34                                  | R1           | -            | IO_34_L13_N        |                    | MRCC_N             |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 58  | FPGA | B34                                  | P6           | -            | IO_34_L19_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 59  | FPGA | B34                                  | J5           | -            | IO_34_L2_P         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 60  | FPGA | B34                                  | P5           | -            | IO_34_L19_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     | ĺ                   |

| 61  | FPGA | B34                                  | J4           | -            | IO_34_L2_N         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 62  | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     | ĺ                   |

| 63  | FPGA | B34                                  | P1           | -            | IO_34_L9_N         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 64  | FPGA | B34                                  | T7           | -            | IO_34_L22_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 65  | FPGA | B34                                  | N1           | -            | IO_34_L9_P         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 66  | FPGA | B34                                  | R7           | -            | IO_34_L22_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 67  | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 68  | FPGA | B34                                  | T5           | -            | IO_34_L21_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 69  | FPGA | B34                                  | K6           | -            | IO_34_L1_N         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 70  | FPGA | B34                                  | R5           | -            | IO_34_L21_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 71  | FPGA | B34                                  | K5           | -            | IO_34_L1_P         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 72  | FPGA | B34                                  | U6           | -            | IO_34_L20_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 73  | FPGA | B34                                  | L5           | -            | IO_34_L6_P         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 74  | FPGA | B34                                  | U5           | -            | IO_34_L20_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 75  | FPGA | B34                                  | M5           | -            | IO_34_L6_N         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 76  | FPGA | B34                                  | V4           | -            | IO_34_L18_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 77  | FPGA | B34                                  | M4           | -            | IO_34_L10_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 78  | FPGA | B34                                  | U4           | -            | IO_34_L18_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 79  | FPGA | B34                                  | N4           | -            | IO_34_L10_N        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 80  | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 81  | FPGA | B34                                  | L4           | -            | IO_34_L5_P         |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| 82  | FPGA | B34                                  | T4           | -            | IO_34_L17_P        |                    |                    |                    |                    |                    |                    |                    |                    |                     |                     |                     |                     |

| Pin | Туре | FPGA<br>Bank or<br>Voltage<br>Domain | FPGA<br>ball | 57xx<br>ball | Signal<br>Option 1 | Signal<br>Option 2 | Signal<br>Option 3 | Signal<br>Option 4 | Signal<br>Option 5 | Signal<br>Option 6 | Signal<br>Option 7 | Signal<br>Option 8  | Signal<br>Option 9 | Signal<br>Option 10 | Signal<br>Option 11 | Signal<br>Option 12 | Signal<br>Option 13 |

|-----|------|--------------------------------------|--------------|--------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|--------------------|---------------------|--------------------|---------------------|---------------------|---------------------|---------------------|

| 83  | FPGA | B34                                  | L3           | -            | IO_34_L5_N         |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 84  | FPGA | B34                                  | Т3           | -            | IO_34_L17_N        |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 85  | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 86  | FPGA | B34                                  | N3           | -            | IO_34_L11_P        |                    | SRCC_P             |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 87  | FPGA | B34                                  | M2           | -            | IO_34_L7_P         |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 88  | FPGA | B34                                  | N2           | -            | IO_34_L11_N        |                    | SRCC_N             |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 89  | FPGA | B34                                  | M1           | -            | IO_34_L7_N         |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 90  | FPGA | B34                                  | V3           | -            | IO_34_L16_P        |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 91  | FPGA | B34                                  | P4           | -            | IO_34_L12_P        |                    | MRCC_P             |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 92  | FPGA | B34                                  | V2           | -            | IO_34_L16_N        |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 93  | FPGA | B34                                  | P3           | -            | IO_34_L12_N        |                    | MRCC_N             |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 94  | FPGA | B34                                  | U2           | -            | IO_34_L15_P        |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 95  | FPGA | B34                                  | K2           | -            | IO_34_L3_P         |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 96  | FPGA | B34                                  | U1           | -            | IO_34_L15_N        |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 97  | FPGA | B34                                  | K1           | -            | IO_34_L3_N         |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 98  | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 99  | FPGA | B34                                  | К3           | -            | IO_34_L4_P         |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 100 | MFIO | 1.8                                  | -            | U6           | RGMII0_TXD0        | RMII0_R<br>XD0     | MII0_RXD0          | VIN2A_D10          | SPI4_CS0           | UART4_RT<br>SN     | PR1_MII0_<br>RXD0  | PR2_PRU1<br>_GPI10  | PR2_PRU1<br>_GPO10 | GPIO5_25            |                     |                     |                     |

| 101 | FPGA | B34                                  | L2           | -            | IO_34_L4_N         |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 102 | MFIO | 1.8                                  | -            | V6           | RGMII0_TXD1        | RMII0_R<br>XD1     | MII0_RXD1          | VIN2A_VS<br>YNC0   | VIN4B_VS<br>YNC1   | SPI4_D0            | UART4_CT<br>SN     | PR1_MII0_<br>RXD1   | PR2_PRU1<br>_GPI9  | PR2_PRU1<br>_GPO9   | GPIO5_24            |                     |                     |

| 103 | GND  |                                      | -            | -            | GND                |                    |                    |                    |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 104 | MFIO | 1.8                                  | -            | U7           | RGMII0_TXD2        | RMII0_R<br>XER     | MII0_RXER          | VIN2A_HS<br>YNC0   | VIN4B_HS<br>YNC1   | SPI4_D1            | UART4_TX<br>D      | PR1_MII0_<br>RXER   | PR2_PRU1<br>_GPI8  | PR2_PRU1<br>_GPO8   | GPIO5_23            |                     |                     |

| 105 | MFIO | 1.8                                  | -            | Y1           | SPI3_D1            | UART3_<br>TXD      | RMII1_RXE<br>R     | MII0_RXCL<br>K     | VIN2A_D2           | VIN4B_D2           | SPI4_CS1           | PR1_MII_M<br>R0_CLK | PR2_PRU1<br>_GPI4  | PR2_PRU1<br>_GPO4   | GPIO5_19            |                     |                     |

| 106 | MFIO | 1.8                                  | -            | V7           | RGMII0_TXD3        | RMII0_C<br>RS      | MII0_CRS           | VIN2A_DE<br>0      | VIN4B_DE<br>1      | SPI4_SCLK          | UART4_RX<br>D      | PR1_MII0_<br>CRS    | PR2_PRU1<br>_GPI7  | PR2_PRU1<br>_GP07   | GPIO5_22            |                     |                     |

| 107 | MFIO | 1.8                                  | -            | V2           | SPI3_SCLK          | UART3_<br>RXD      | RMII1_CRS          | MII0_RXDV          | VIN2A_D1           | VIN4B_D1           | PR1_MII0_<br>RXDV  | PR2_PRU1<br>_GPI3   | PR2_PRU1<br>_GPO3  | GPIO5_18            |                     |                     |                     |

| 108 | MFIO | 1.8                                  | -            | W9           | RGMII0_TXC         | UART3_<br>CTSN     | RMII1_RXD<br>1     | MII0_RXD3          | VIN2A_D3           | VIN4B_D3           | SPI3_D0            | SPI4_CS2            | PR1_MII0_<br>RXD3  | PR2_PRU1<br>_GPI5   | PR2_PRU1<br>_GPO5   | GPI05_20            |                     |

| 109 | MFIO | 3.3                                  | -            | Y9           | MMC1_SDWP          | UART6_<br>TXD      | I2C4_SCL           | GPIO6_28           |                    |                    |                    |                     |                    |                     |                     |                     |                     |

| 110 | MFIO | 1.8                                  | -            | V9           | RGMII0_TXCTL       | UART3_<br>RTSN     | RMII1_RXD<br>0     | MII0_RXD2          | VIN2A_D4           | VIN4B_D4           | SPI3_CS0           | SPI4_CS3            | PR1_MII0_<br>RXD2  | PR2_PRU1<br>_GPI6   | PR2_PRU1<br>_GPO6   | GPI05_21            |                     |

Page 14 of 47

| Pin | Туре | FPGA<br>Bank or<br>Voltage<br>Domain | FPGA<br>ball | 57xx<br>ball | Signal<br>Option 1 | Signal<br>Option 2 | Signal<br>Option 3 | Signal<br>Option 4 | Signal<br>Option 5 | Signal<br>Option 6  | Signal<br>Option 7 | Signal<br>Option 8 | Signal<br>Option 9 | Signal<br>Option 10 | Signal<br>Option 11 | Signal<br>Option 12 | Signal<br>Option 13 |

|-----|------|--------------------------------------|--------------|--------------|--------------------|--------------------|--------------------|--------------------|--------------------|---------------------|--------------------|--------------------|--------------------|---------------------|---------------------|---------------------|---------------------|

| 111 | MFIO | 1.8                                  | -            | C14          | PR2_MDIO_MDCLK     | MCASP1<br>_ACLKX   | VIN6A_FLD<br>0     | I2C3_SDA           | PR2_PRU1<br>_GPI7  | PR2_PRU1<br>_GP07   | GPI07_31           |                    |                    |                     |                     |                     |                     |

| 112 | GND  | -                                    | -            | -            | GND                |                    |                    |                    |                    |                     |                    |                    |                    |                     |                     |                     |                     |

| 113 | MFIO | 1.8                                  | -            | D14          | PR2_MDIO_DATA      | MCASP1<br>_FSX     | VIN6A_DE<br>0      | I2C3_SCL           | GPI07_30           |                     |                    |                    |                    |                     |                     |                     |                     |

| 114 | MFIO | 1.8                                  | -            | V4           | RGMII0_RXD3        | RMII1_T<br>XD0     | MII0_TXD2          | VIN2A_D7           | VIN4B_D7           | PR1_MII0_<br>TXD2   | PR2_PRU1<br>_GPI13 | PR2_PRU1<br>_GPO13 | GPIO5_28           |                     |                     |                     |                     |

| 115 | MFIO | 1.8                                  | -            | G16          | UART4_RXD          | MCASP4<br>_AXR0    | SPI3_D0            | UART8_CT<br>SN     | VOUT2_D1<br>8      | VIN4A_D18           | VIN5A_D13          |                    |                    |                     |                     |                     |                     |

| 116 | MFIO | 1.8                                  | -            | V3           | RGMII0_RXD2        | RMII0_T<br>XEN     | MII0_TXEN          | VIN2A_D8           | PR1_MII0_<br>TXEN  | PR2_PRU1<br>_GPI14  | PR2_PRU1<br>_GPO14 | GPIO5_29           |                    |                     |                     |                     |                     |

| 117 | MFIO | 1.8                                  | -            | E12          | MCASP4_AXR2        | MCASP1<br>_AXR4    | VOUT2_D4           | VIN4A_D4           | GPIO5_6            |                     |                    |                    |                    |                     |                     |                     |                     |

| 118 | MFIO | 1.8                                  | -            | Y2           | RGMII0_RXD1        | RMII0_T<br>XD1     | MII0_TXD1          | VIN2A_D9           | PR1_MII0_<br>TXD1  | PR2_PRU1<br>_GPI15  | PR2_PRU1<br>_GPO15 | GPIO5_30           |                    |                     |                     |                     |                     |

| 119 | MFIO | 1.8                                  | -            | D17          | MCASP4_AXR1        | SPI3_CS<br>0       | UART8_RT<br>SN     | UART4_TX<br>D      | VOUT2_D1<br>9      | VIN4A_D19           | VIN5A_D12          | PR2_PRU1<br>_GPI0  | PR2_PRU1<br>_GPO0  |                     |                     |                     |                     |

| 120 | MFIO | 1.8                                  | -            | W2           | RGMII0_RXD0        | RMII0_T<br>XD0     | MII0_TXD0          | VIN2A_FLD<br>0     | VIN4B_FLD<br>1     | PR1_MII0_<br>TXD0   | PR2_PRU1<br>_GPI16 | PR2_PRU1<br>_GPO16 | GPI05_31           |                     |                     |                     |                     |

| 121 | MFIO | 1.8                                  | -            | C18          | MCASP4_ACLKX       | MCASP4<br>_ACLKR   | SPI3_SCLK          | UART8_RX<br>D      | I2C4_SDA           | VOUT2_D1<br>6       | VIN4A_D16          | VIN5A_D15          |                    |                     |                     |                     |                     |

| 122 | MFIO | 1.8                                  | -            | V5           | RGMII0_RXCTL       | RMII1_T<br>XD1     | MII0_TXD3          | VIN2A_D6           | VIN4B_D6           | PR1_MII0_<br>TXD3   | PR2_PRU1<br>_GPI12 | PR2_PRU1<br>_GPO12 | GPI05_27           |                     |                     |                     |                     |

| 123 | MFIO | 1.8                                  | -            | A21          | MCASP4_FSX         | MCASP4<br>_FSR     | SPI3_D1            | UART8_TX<br>D      | I2C4_SCL           | VOUT2_D1<br>7       | VIN4A_D17          | VIN5A_D14          |                    |                     |                     |                     |                     |

| 124 | MFIO | 1.8                                  | -            | U5           | RGMII0_RXC         | RMII1_T<br>XEN     | MII0_TXCL<br>K     | VIN2A_D5           | VIN4B_D5           | PR1_MII_M<br>T0_CLK | PR2_PRU1<br>_GPI11 | PR2_PRU1<br>_GPO11 | GPIO5_26           |                     |                     |                     |                     |

| 125 | FPGA | 1.8                                  | F12          | -            | FPGA_DONE          |                    |                    |                    |                    |                     |                    |                    |                    |                     |                     |                     |                     |

| 126 | KEY  | -                                    | -            | -            |                    |                    |                    |                    |                    |                     |                    |                    |                    |                     |                     |                     |                     |

| 127 | KEY  | -                                    | -            | -            |                    |                    |                    |                    |                    |                     |                    |                    |                    |                     |                     |                     |                     |