# MitySOM-5CSx Design Guide

# **1** Overview

The MitySOM-5CSx family of modules are designed to take most of the pain out of developing a new product based on the Altera Cyclone V FPGAs that include ARM processing core[s]. The long list of requirements and costly board design specifications are handled by the module wherever possible. This, along with the board support package, makes it possible to quickly create new products with greatly reduced effort relative to creating a complete system design from scratch.

| Facts                                  | MitySOM-5CSx                                                                                                                                                         |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Required socket connector              | MXM Connector, JAE MM70-314-310B1-1-R300 or equivalent                                                                                                               |

| Input voltage Required                 | 5V                                                                                                                                                                   |

| Memory Peripherals (On Module)         | EEPROM, QSPI NOR Flash, DDR3L SDRAM                                                                                                                                  |

| On-Module HPS Peripherals <sup>1</sup> | $USB_1$ , $UART_0$ , $I^2C_0$                                                                                                                                        |

| HPS Edge Peripherals <sup>2</sup>      | EMAC <sub>1</sub> , USB <sub>0</sub> , CAN <sub>0,1</sub> , MMC/SD/SDIO <sub>0</sub> , I <sup>2</sup> C <sub>1,3</sub> , SPIM <sub>0</sub> , and SPIS <sub>0,1</sub> |

| HPS Fabric Peripherals <sup>3</sup>    | EMAC <sub>0,1</sub> , USB <sub>0</sub> , CAN <sub>0,1</sub> , UART <sub>1</sub> , MMC/SD/SDIO <sub>0</sub> , I <sup>2</sup> C <sub>2</sub> , and SPIM <sub>0,1</sub> |

| Total number of FPGA I/Os              | 107 / 133                                                                                                                                                            |

| Differential I/Os                      | 47 pairs / 60 pairs                                                                                                                                                  |

| Clock Differential I/Os                | 7 pairs                                                                                                                                                              |

| Exclusively Single Ended I/Os          | 7                                                                                                                                                                    |

# **1.1 Fast Facts for Getting Started**

The table above gives an idea of the peripherals and features available on the MitySOM. Additional details can be found in the list below with the HPS peripherals grouped by the FPGA Bank.

- Bank7A includes a mix of module peripherals and exposed HPS peripherals (+3.3V)

- $\circ~$  UART\_0 Console Interface (by default in BSP)

- $\circ~I^2C_0$  is used on the module for: EEPROM, RTC, Temperature Sensor, Debug LED Driver

- TRACE Peripheral can be directed to the debug header or the edge connector

- With the JTAG/TRACE adapter in TRACE Mode, the TRACE pins are used on the module

- + Under normal use, the TRACE pins (other peripherals) go to the edge connector as:  $\diamond~SPIS_0$  / GPIOs

- ♦ SPIS<sub>1</sub> / GPIOs / CAN<sub>1</sub>

- $\circ~SPIM_0$  /  $I^2C_1$  / UART\_0 Flow Control / CAN1 / GPIOs

- $\circ$  CAN<sub>0</sub> / GPIOs

- 25MHz HPS-CLK1 oscillator

- HPS-CLK2 available through Edge Connector

- $\circ$  HPS-PORSEL = Fast to support CvP

- $\,\circ\,$  Reset I/O Connections drive with open collector or open emitter

- **Bank7C** is exposed to the edge connector (+3.3V I/O) and supports:

$<sup>^{1}</sup>$ These HPS peripherals are on the module and must be chosen as the pin MUX option. The UART<sub>0</sub> pins are used by the console and are available on the Edge Connector – they are only supported at the default location.

$<sup>^{2}</sup>$ HPS Peripherals have very limited MUX options to choose the desired mix of peripherals. If an HPS peripheral choice blocks another desired peripheral, it can be accessed through the FPGA fabric. All these HPS Edge Pins can also be used for simple GPIO pins.

$<sup>^{3}</sup>$ These HPS peripherals can be accessed through the FPGA fabric and will consume some of the available I/O pins if used in this manner. If they are not listed as HPS Edge Peripherals<sup>2</sup>, they can only be accessed through the FPGA fabric.

- SDMMC x4 or x8

- $\circ$  USB<sub>0</sub>

- GPIOs

- **Bank7B** and **Bank7D** share a common VIO (+1.8V to save power)

- $\circ~$  +VIO1.8V is provided by the module for the I/O supply

- $\circ~$  **Bank7B** uses the QSPI1 peripheral for NOR flash on the SOM

- $^\circ~Bank7B$  remaining pins go to the edge connector for other peripherals such as Ethernet

- $\circ~\textbf{Bank7D}$  uses the  $\text{USB}_1$  peripheral, with the ULPI USB Phy on the SOM

There are three peripherals locked down on the MitySOM-5CSx. These were assigned to HPS peripheral locations while trying to maintain flexibility. The QSPI NOR Flash interface is only available in one location, and the included  $USB_1$  peripheral was assigned to allow an external SDMMC interface. With those assigned, there are very few options for the required UART and I<sup>2</sup>C peripherals. This leaves some serial peripherals and a mix of Ethernet, SD/MMC, NAND, USB, and GPIOs available for the end application to pick the desired mix.

# 1.2 MitySOM-5CSx Family Modules

The MitySOM-5CSx family of modules is available in a few configurations. These options provide a range of FPGA fabric and memory sizes to meet a range of applications. See the table below for a high level overview of the module configurations. More options may be available in the future, and additional options can be discussed with Critical Link if desired. The various module configurations are pin compatible. The initial range of module configurations is listed in Table 1. The I/O counts for each module configuration is listed in Table 2.

| Feature            | 5CSE-L2-3YA  | 5CSE-H4-3YA  | 5CSX-H5-4YA  | 5CSX-H6-42A  | 5CSX-H6-53B  |

|--------------------|--------------|--------------|--------------|--------------|--------------|

| Temperature Range  | C & I        | Ι            | Ι            | C & I        | C & I        |

| ARM Cores / Speed  | 1 / 600MHz   | 2 / 800MHz   | 2 / 800MHz   | 2 / 800MHz   | 2 / 800MHz   |

| Transceivers       | 0            | 0            | 6            | 6            | 6            |

| FPGA Fabric        | 25kLE        | 40kLE        | 85kLE        | 110kLE       | 110kLE       |

| FPGA DDR           | 0MB          | 0MB          | 0MB          | 256MB        | 512MB        |

| HPS DDR            | 512MB        | 1GB+ECC      | 1GB+ECC      | 1GB+ECC      | 2GB+ECC      |

| QSPI NOR Flash     | 16MB         | 16MB         | 32MB         | 32MB         | 48MB         |

| EEPROM             | 16Kb         | 16kb         | 16kb         | 16kb         | 16kb         |

| Temperature Sensor | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| RTC                | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| RGB Debug LED      | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| Debug LED          | Green        | Green        | Green        | Green        | Green        |

| Power LED          | Green        | Green        | Green        | Green        | Green        |

| HPS CLK1           | 25MHz        | 25MHz        | 25MHz        | 25MHz        | 25MHz        |

| CvP Supported      |              |              | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| FPP Config x16     | $\sqrt{4}$   | $\sqrt{4}$   | $\sqrt{4}$   |              |              |

Table 1: MitySOM-5CSx Features

$^{4}\mbox{The}$  additional pins required to support FPP are available on the module versions with expanded I/Os replacing the FPGA DDR connections.

$^{5}$ The FPGA DDR I/Os are on the module. The expanded I/O versions without FPGA DDR memory make 26 of these pins available on the edge connector.

| Table 2:              | <u> </u> |     |             |     |     |            |

|-----------------------|----------|-----|-------------|-----|-----|------------|

| I/O Counts            | B3B      | B4A | <b>B0/1</b> | B3A | B5A | <b>B5B</b> |

| 5CSX-H6-42A           |          |     |             |     |     |            |

| GXB Pairs RX/TX/CLK   |          |     | 6/6/2       |     |     |            |

| FPGA IOs 3B           | 32       |     |             |     |     |            |

| FPGA IOs 4A           |          | 64  |             |     |     |            |

| PERST#                |          |     |             |     | 1   |            |

| FPGA DDR <sup>5</sup> |          |     |             | 16  | 15  | 7          |

| 5CSX-H6-53B           |          |     |             |     |     |            |

| GXB Pairs             |          |     | 6/6/2       |     |     |            |

| FPGA IOs 3B           | 32       |     |             |     |     |            |

| FPGA IOs 4A           |          | 64  |             |     |     |            |

| PERST#                |          |     |             |     | 0   |            |

| FPGA DDR <sup>5</sup> |          |     |             | 16  | 16  | 7          |

| 5CSE-L2-3YA           |          |     |             |     |     |            |

| GXB Pairs             |          |     | 0           |     |     |            |

| FPGA IOs 3B           | 32       |     |             |     |     |            |

| FPGA IOs 4A           |          | 64  |             |     |     |            |

| PERST#                |          |     |             |     | 1   |            |

| FPGA IOs 3A/5A/5B     |          |     |             | 16  | 10  | 0          |

| 5CSE-H4-3YA           |          |     |             |     |     |            |

| GXB Pairs             |          |     | 0           |     |     |            |

| FPGA IOs 3B           | 32       |     |             |     |     |            |

| FPGA IOs 4A           |          | 64  |             |     |     |            |

| PERST#                |          |     |             |     | 1   |            |

| FPGA IOs 3A/5A/5B     |          |     |             | 16  | 10  | 0          |

| 5CSX-H5-4YA           |          |     |             |     |     |            |

| GXB Pairs             |          |     | 6/6/2       |     |     |            |

| FPGA IOs 3B           | 32       |     |             |     |     |            |

| FPGA IOs 4A           |          | 64  |             |     |     |            |

| PERST#                |          |     |             |     | 1   |            |

| FPGA IOs 3A/5A/5B     |          |     |             | 16  | 10  | 0          |

| 5CSX-H6-4YA           |          |     |             |     |     |            |

| GXB Pairs             |          |     | 6/6/2       |     |     |            |

| FPGA IOs 3B           | 32       |     |             |     |     |            |

| FPGA IOs 4A           |          | 64  |             |     |     |            |

| PERST#                |          |     |             |     | 1   | -          |

| FPGA IOs 3A/5A/5B     |          |     |             | 16  | 10  | 0          |

#### - - -

# **1.3 Module Dimensions**

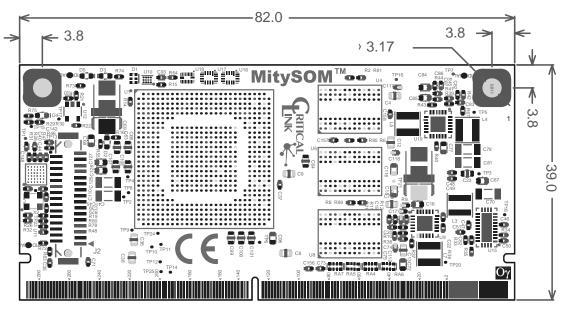

The MitySOM-5CSx modules measure 82mm x 39mm. A dimmensioned drawing of the module is shown in Figure 1. All dimensions shown are in milimeters.

### **1.4 Thermal Performance**

Most designs will need some form of additional heatsink or active cooling to maintain the junction temperature within device limits. A fully loaded design will require significant cooling to operate reliably

Figure 1: MitySOM-5CSx Mechanical Drawing

across the full commercial or industrial temperature range.

Designs that are not pushing the capabilities of the CycloneV and HPS performance can use various strategies to limit the power consumed. Some typical strategies to persue are running the HPS core clock frequency at a reduced rate. The MitySOM modules default to the 800MHz HPS operating frequency. Setting this to a slower clock rate will reduce the dynamic power consumption. The static power consumption is based on the leakage of the internal features and cannot be reduced easily.

When designing the FPGA logic, design choices play an important role in determining the power consumed. Faster clocks will consume more power proportional to the clock rate. Isolating the fast logic sections of a design and running logic slower where possible will provide a few benefits. Some of the benefits include reduced power consumption, and quicker compiles. At fast clock rates, the Quartus tools will have to work harder to meet timing. If the tools have difficuly in meeting timing, this will generally require longer design compiles. Altera has an application note, see AN:531<sup>6</sup> for additional details.

Fast I/O pins will also consume more power. If fast interfaces are desired, reduce the voltage standard where possible. Also reduce the capacitive load on the I/O connections in PCB layout. The dynamic power requirements increase linearly with the capacitance an I/O has to charge and discharge at each transition. The voltage is more significant because this term is expoenetial. The power required to drive an I/O pin is generally  $P_{dyn} = 1/2CV^2 f$ . Checking various design scenarios is easily performed with the Early Power Estimator<sup>7</sup> and entering the I/O characteristics into the fields on the spreadsheet for each group of signals to get an estimate. As a design progresses, Quartus design details can be loaded into the EPE to get better estimates of power requirements.

Altera also has a Webcast<sup>8</sup> for getting an overview of power reductions on the 28nm devices, such as the Cyclone V used on the MitySOM-5CSx. The related White paper<sup>9</sup> can also be reviewed to get an

<sup>&</sup>lt;sup>6</sup>http://www.altera.com/content/dam/altera-www/global/en\_US/pdfs/literature/an/an531.pdf

<sup>&</sup>lt;sup>7</sup>https://www.altera.com/support/support-resources/devices/power/cy4-5-estimator.html

<sup>&</sup>lt;sup>8</sup>http://www.altera.com/education/webcasts/all/wc-2010-lower-power-28nm.html

<sup>9</sup>http://www.altera.com/content/dam/altera-www/global/en\_US/pdfs/literature/wp/wp-01148-stxv-power-consumption. pdf

overview of the power saving features in the FPGA.

# 2 Connectors

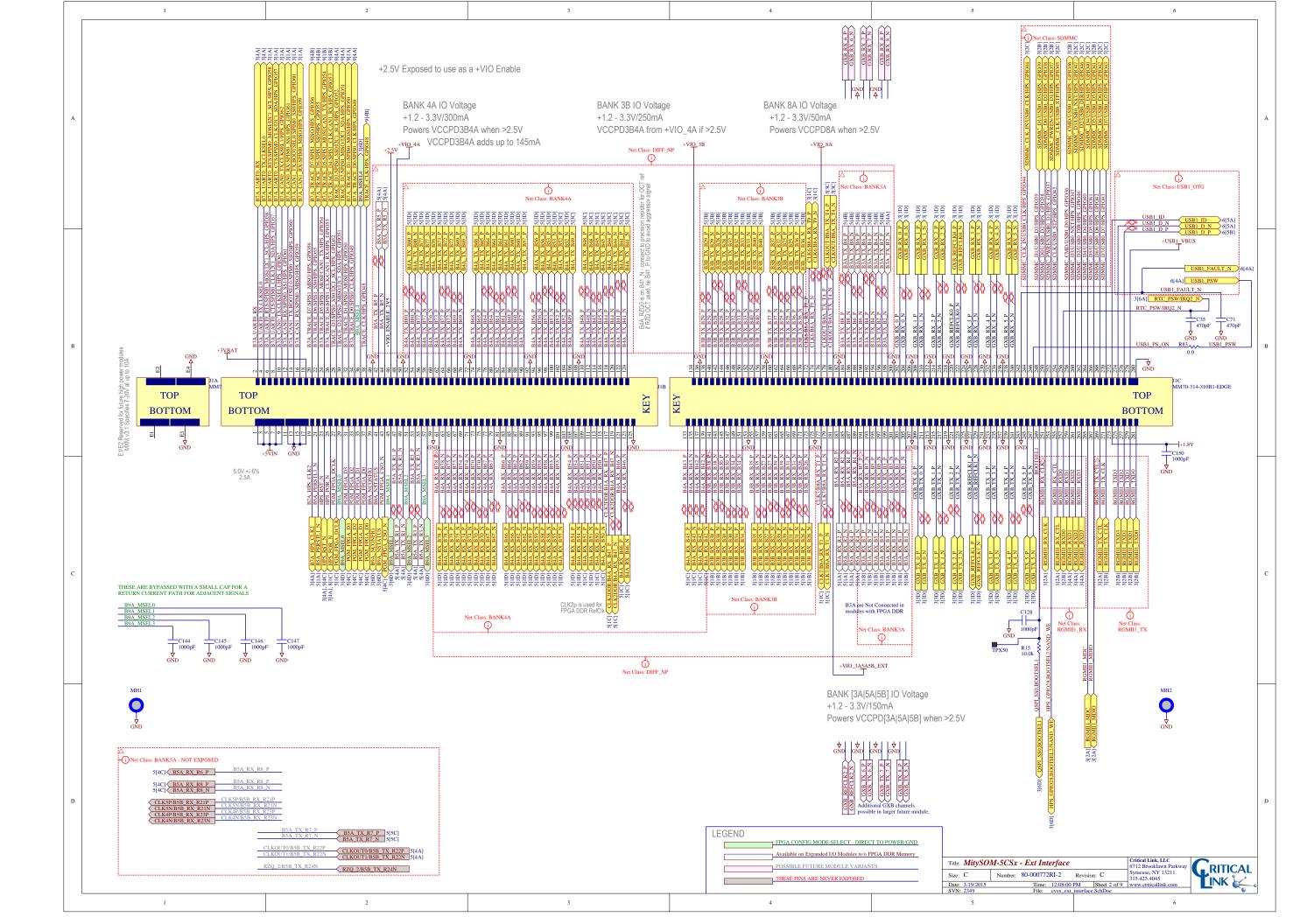

# 2.1 MitySOM-5CSx Module Card Edge Pin-out

The MitySOM-5CSx uses the MXM standard connector for the edge connector interface. The module only uses the physical interface, and does not match the MXM electrical interface. Attempting to use the MitySOM in a MXM host is likely to damage one or both boards.

The MitySOM-5CSx family uses an MXM connector and general footprint with one exception – the double pin at the end has been separated into two individual pins numbered 278 and 280.

Note that the modules are NOT compatible with the MXM electrical standard... signal assignments, VIO voltages, etc. Intermixing modules/sockets from the two standards would very possibly cause permanent damage to one or both sides.

#### 2.1.1 Top Edge Connector

At the end of the module are pins that are ganged together. These are ganged to match the MXM standard's<sup>10</sup> ganged pins. The first set of ganged pins is reserved for possible future high power modules.

| PIN | TYPE | SIGNAL | GROUP |

|-----|------|--------|-------|

| E2  | RSVD |        | Power |

|     | GAP  | NC     |       |

|     | GAP  | NC     |       |

| E4  | PWR  | GND    | Power |

| E4  | PWR  | GND    | Power |

| E4  | PWR  | GND    | Power |

| E4  | PWR  | GND    | Power |

| E4  | PWR  | GND    | Power |

| E4  | PWR  | GND    | Power |

| E4  | PWR  | GND    | Power |

| E4  | PWR  | GND    | Power |

| E4  | PWR  | GND    | Power |

#### Table 3: Top Edge Power

$^{10}$ There is one difference between the ganged pins of the MXM specification and the MitySOM-5CSx's edge connector. At the high end of the connector in the MXM specification, there are two pins tied together. In the MitySOM these are separate pins numbered 278 and 280. The edge connector pins are uniformly spaced at 0.5mm pitch.

After the power pins, there is a group of HPS peripheral pins. These are generally used as serial interfaces, but are available as HPS GPIO pins as well. The default console serial interface is included here.

| PIN | Ball | TYPE | SIGNAL                                       | GROUP       |

|-----|------|------|----------------------------------------------|-------------|

| 2   | B19  | Ι    | B7A_UART0_RX                                 | Bank7A      |

| 4   | C16  | I/O  | B7A_UART0_TX,CLKSEL0                         | Bank7A,CSEL |

| 6   | C17  | I/O  | B7A_UART0_RTS/SPIM0_MOSI/I2C1_SCL/HPS_GPIO58 | Bank7A      |

| 8   | A18  | I/O  | B7A_UART0_CTS/SPIM0_CLK/I2C1_SDA/HPS_GPIO57  | Bank7A      |

| 10  | H17  | I/O  | B7A_CAN0_TX,CLKSEL1/HPS_GPIO62               | Bank7A,CSEL |

| 12  | A17  | I/O  | B7A_CAN0_RX/SPIM0_SS1/HPS_GPIO61             | Bank7A      |

| 14  | J17  | I/O  | B7A_CAN1_TX,BOOTSEL0/SPIM0_SS0/HPS_GPIO60    | Bank7A,BSEL |

| 16  | B18  | I/O  | B7A_CAN1_RX/SPIM0_MISO/HPS_GPIO59            | Bank7A      |

| 18  | D7   | PWR  | VBAT+3V <sup>11</sup>                        | Power       |

Table 4: Top Edge HPS Bank7A Peripheral I/O Pins

On the MitySOM-5CSx, two of the simple serial interfaces are consumed. The main console UART is assigned by default to pins C16 and B19 for receive and transmit. There is generally no flow control required on the console interface. The  $I^2C_0$  is consumed on the module to control a number of devices. This is assigned to pins B16 and C19 on the U23 package. The  $I^2C_0$  interface controls the factory configuration EEPROM, the AB1803-T3 RTC, a LM73<sup>12</sup> temperature sensor, and the LP5562TMX debug LED driver to light the RGB LED and a green debug LED. The second UART peripheral, UART<sub>1</sub>, could only be exposed on the pins consumed by the  $I^2C_0$  interface. If the second UART is desired, it must be routed through the FPGA fabric.

The remaining Bank7A peripherals can be assigned as desired. The assignment options are listed in Table 5. If flow control is desired, it can be enabled for the console UART. Note that some of the Bank7A group of pins are also assigned to the BSEL and CSEL groups. The pins in the BSEL and CSEL groups are read at reset to identify the desired boot selection and clock divisor. The HPS\_CLK1 is on the module and has a 25MHz oscillator – this is the reference clock during initial boot.

$<sup>^{11}</sup>$ The VBAT+3V input powers the RTC chip and V<sub>CCBAT</sub> pin of the Cyclone V. If you do not use the design security feature in Cyclone V devices or need the RTC to maintain the time, connect to a 2.5V, or 3.0V power supply. The power-on reset (POR) circuitry monitors VCCBAT. Cyclone V devices do not exit POR if VCCBAT is not powered up.

$<sup>^{12}</sup>$ The original production version of the MitySOM-5CSX included a TC74A5 for the temperature sensor. Due to manufacturing fallout, the temperature sensor has been replaced with an LM73CIMK-1. These sensors reside at different I<sup>2</sup>C addresses.

| Table 50 | Ton Edge | e HPS Bank7      | ∆ Perinhera   | l Details |

|----------|----------|------------------|---------------|-----------|

| Tuble 5. | TOP Luge | / III O Dullin / | a i oripiioru | Dotuns    |

| EDGE | BALL | TYPE | Description                                                              |  |  |  |

|------|------|------|--------------------------------------------------------------------------|--|--|--|

| 2    | B19  | Ι    | Console UART0 receive data                                               |  |  |  |

| 4    | C16  | 0    | Console UART0 transmit data. CLKSEL0 value is read at reset,             |  |  |  |

|      |      | Ι    | set with a pull-up or pull-down resistor of 1K $\Omega$ to 10K $\Omega$  |  |  |  |

| 6    | C17  | 0    | UART0_RTS – flow control is generally not required for the console UART. |  |  |  |

|      |      | 0    | SPIM0_MOSI – SPI Master Data Out                                         |  |  |  |

|      |      | I/O  | I <sup>2</sup> C1_SCL                                                    |  |  |  |

|      |      | I/O  | HPS_GPIO58                                                               |  |  |  |

| 8    | A18  | Ι    | UART0_CTS – flow control is generally not required for the console UART. |  |  |  |

|      |      | 0    | SPIM0_CLK – SPI Master Clock                                             |  |  |  |

|      |      | I/O  | I <sup>2</sup> C1_SDA                                                    |  |  |  |

|      |      | I/O  | HPS_GPIO57                                                               |  |  |  |

| 10   | H17  | 0    | CAN0_TX                                                                  |  |  |  |

|      |      | Ι    | CLKSEL1 – value read at reset                                            |  |  |  |

|      |      | I/O  | HPS_GPIO62                                                               |  |  |  |

| 12   | A17  | Ι    | CAN0_RX                                                                  |  |  |  |

|      |      | 0    | SPIM0_SS1                                                                |  |  |  |

|      |      | I/O  | HPS_GPIO61                                                               |  |  |  |

| 14   | J17  | 0    | CAN1_TX                                                                  |  |  |  |

|      |      | Ι    | BOOTSEL0 – value read at reset                                           |  |  |  |

|      |      | 0    | SPIM0_SS0                                                                |  |  |  |

|      |      | I/O  | HPS_GPIO60                                                               |  |  |  |

| 16   | B18  | Ι    | CAN1_RX                                                                  |  |  |  |

|      |      | Ι    | SPIM0_MISO                                                               |  |  |  |

|      |      | I/O  | HPS_GPIO59                                                               |  |  |  |

| 18   |      | PWR  | Battery back-up power supply                                             |  |  |  |

|      |      |      | (For RTC and design security volatile key register)                      |  |  |  |

Table 6: Top Edge HPS Bank7A MUXed Debug Peripheral I/O Pins

| PIN | Ball | TYPE | SIGNAL                                     | GROUP        |

|-----|------|------|--------------------------------------------|--------------|

| 20  | C18  | I/O  | B7A_TRACE_D7/SPIS1_MISO/HPS_GPIO56         | Bank7A-MUXed |

| 22  | A19  | I/O  | B7A_TRACE_D6/SPIS1_SS0/HPS_GPIO55          | Bank7A-MUXed |

| 24  | J18  | I/O  | B7A_TRACE_D5/SPIS1_MOSI/CAN1_TX/HPS_GPIO54 | Bank7A-MUXed |

| 26  | A20  | I/O  | B7A_TRACE_D4/SPIS1_CLK/CAN1_RX/HPS_GPIO53  | Bank7A-MUXed |

| 28  | K18  | I/O  | B7A_TRACE_D3/SPIS0_SS0/HPS_GPIO52          | Bank7A-MUXed |

| 30  | A21  | I/O  | B7A_TRACE_D2/SPIS0_MISO/HPS_GPIO51         | Bank7A-MUXed |

| 32  | B21  | I/O  | B7A_TRACE_D1/SPIS0_MOSI/HPS_GPIO50         | Bank7A-MUXed |

| 34  | A22  | I/O  | B7A_TRACE_D0/SPIS0_CLK/HPS_GPIO49          | Bank7A-MUXed |

| 36  | K9   | Ι    | B9A_MSEL4                                  | MSEL         |

| 38  | C21  | Ι    | B7A_TRACE_CLK/HPS_GPIO_48                  | Bank7A-MUXed |

| 40  |      | PWR  | GND                                        | Power        |

The Bank7A-MUXed group of signals includes the TRACE<sup>13</sup> peripheral. This group will generally provide the most benefit for debug or some additional GPIO pins. The debug connector on the MitySOM module provides a means to have the TRACE peripheral routed to the debug peripheral instead of the edge connector when the debug adapter is connected. This eliminates the need to include the Mictor TRACE connector on the carrier board merely to support debug efforts. The debug board can operate in JTAG-chain mode and leave the Bank7A-MUXed pins routed to the edge connector, or be manually set into the TRACE debug mode and route the TRACE connections to the Mictor TRACE connector on the debug adapter.

The TRACE peripheral pins are routed through bidirectional analog MUXes on the MitySOM. These are fast enough to support the maximum speed of the SPI Slave peripherals that could be assigned to those pins, running as fast as 50MHz or the GPIOs, which have a minimum detectable pulse width of 2us, based on a debounce clock frequency of 1MHz. The CAN peripheral has a maximum data rate of 1Mbps, and the  $I^2C$  interfaces top out at 500KHz.

| PIN | Ball | TYPE | Description                        |  |

|-----|------|------|------------------------------------|--|

| 20  | C18  | 0    | TRACE_D7                           |  |

|     |      | 0    | SPIS1_MISO – SPI Slave Data Output |  |

|     |      | I/O  | HPS_GPIO56                         |  |

| 22  | A19  | 0    | TRACE_D6                           |  |

|     |      | Ι    | SPIS1_SS0 – SPI Slave Select       |  |

|     |      | I/O  | HPS_GPIO55                         |  |

| 24  | J18  | 0    | TRACE_D5                           |  |

|     |      | Ι    | SPIS1_MOSI – SPI Slave Data Input  |  |

|     |      | 0    | CAN1_TX                            |  |

|     |      | I/O  | HPS_GPIO54                         |  |

| 26  | A20  | 0    | TRACE_D4                           |  |

|     |      | Ι    | SPIS1_CLK – SPI Slave Clock Input  |  |

|     |      | Ι    | CAN1_RX                            |  |

|     |      | I/O  | HPS_GPIO53                         |  |

| 28  | K18  | 0    | TRACE_D3                           |  |

|     |      | Ι    | SPIS0_SS0 – SPI Slave Select Input |  |

|     |      | I/O  | I2C1_SCL                           |  |

|     |      | I/O  | HPS_GPIO52                         |  |

| 30  | A21  | 0    | TRACE_D2                           |  |

|     |      | 0    | SPIS0_MISO – SPI Slave Data Output |  |

|     |      | I/O  | HPS_GPIO51                         |  |

|     |      | I/O  | I2C1_SDA                           |  |

| 32  | B21  | 0    | TRACE_D1                           |  |

|     |      | Ι    | SPIS0_MOSI – SPI Slave Data Input  |  |

|     |      | I/O  | HPS_GPIO50                         |  |

| 34  | A22  | 0    | TRACE_D0                           |  |

|     |      | Ι    | SPIS0_CLK – SPI Slave Clock Input  |  |

|     |      | I/O  | HPS_GPIO49                         |  |

| 36  | K9   | Ι    | MSEL4 – value read at power-on     |  |

| 38  | C21  | 0    | TRACE_CLK – Trace Clock Output     |  |

|     |      | I/O  | HPS_GPIO48                         |  |

Table 7: Top Edge HPS Bank7A-MUXed Peripheral Details

<sup>13</sup>http://www.altera.com/content/dam/altera-www/global/en\_US/pdfs/literature/hb/cyclone-v/cv\_54007.pdf Core-Sight Debug and Trace. Note that TRACE can be run over JTAG as well.

$\mathbf{P}$

| Table 8: Top Edge Bank5A Expanded I/O Pins |      |      |                          |           |  |

|--------------------------------------------|------|------|--------------------------|-----------|--|

| PIN                                        | BALL | TYPE | SIGNAL                   | GROUP     |  |

| 42                                         | AC24 | I/O  | NC,B5A_TX_R5_P/DEV_OE    | NC,Bank5A |  |

| 44                                         | AB23 | I/O  | NC,B5A TX R5 N/DEV CLR N | NC,Bank5A |  |

The general FPGA I/O pins are assigned signal names based on the 110KLE Cyclone V device. They are also assigned signal names according to the highest achievable performance. For each differential pair, there is a SERDES block in hard IP that can operate in a single direction. To make use of the greatest level of performance on these I/Os, connect the Bank4A pairs as transmit pairs using the SERDES blocks.

These pins can all be used as input pins, output pins, or bidirectional pins if the SERDES block is not required. Many of the signals can also operate as Emulated LVDS Output channels, but note that some of the signals do not have a complete pair. On the U23 package used on the MitySOM, not all the signals are paired up, such as B76\_N and B57\_P. Many of these pins can also be used for various DDR memory interfaces and connect to the Hard Memory Controller. Please refer to the Altera pin assignment spreadsheet for these assignment options. The FPGA used on the MitySOM-5CSx is the U23 package with 672 pins.

The smaller MitySOM-5CSE does not include the Hard Memory Controller. It also gives up the seven pins of Bank5B that are used by the FPGA DDR interface on the MitySOM. Other than that and the obviously missing high speed transceivers, the designs can migrate to larger or smaller options as desired. Note that the pin assignments remain the same on the smaller devices, size A2 to A4, but the signal names and pair numbering is not the same. The larger size 5 and 6 FPGAs use the signal name assignments detailed in the MitySOM design documents.

One of the Bank4A pins, pin AH7 can also be used for the termination resistor reference current. If using an I/O standard that requires calibrated on-chip terminations, connect the required resistor to the RZQ pin. If using a MitySOM-5CSx with the FPGA DDR memory, there is an RZQ reference with a  $240\Omega$  resistor on pin AB25. In some designs this RZQ reference connection can be shared.

$<sup>^{14}\</sup>mbox{The VREF4AN0}$  is half the externally supplied VIO\_4A voltage.

| PIN      | Ball | <b>TYPE</b> | age FPGA Bank4A 1/O PI<br>SIGNAL | GROUP            |

|----------|------|-------------|----------------------------------|------------------|

|          | Dall |             | GND                              |                  |

| 46<br>48 |      | PWR<br>PWR  | +VIO $4A^{14}$                   | Power            |

|          |      | PWR         | -                                | Power            |

| 50<br>52 | AF27 | I/O         | GND<br>B4A TX B80 P              | Power<br>Demla44 |

|          |      |             |                                  | Bank4A           |

| 54       | AF28 | I/O         | B4A_TX_B80_N                     | Bank4A           |

| 56       | AG28 | I/O         | B4A_TX_B77_P                     | Bank4A           |

| 58       | AH27 | I/O         | B4A_TX_B77_N                     | Bank4A           |

| 60       | AH26 | I/O         | B4A_TX_B76_N                     | Bank4A           |

| 62       | AG26 | I/O         | B4A_TX_B73_P                     | Bank4A           |

| 64       | AG24 | I/O         | B4A_TX_B72_P                     | Bank4A           |

| 66       | AH24 | I/O         | B4A_TX_B72_N                     | Bank4A           |

| 68       | AH23 | I/O         | B4A_TX_B69_P                     | Bank4A           |

| 70       | AH22 | I/O         | B4A_TX_B69_N                     | Bank4A           |

| 72       |      | PWR         | GND                              | Power            |

| 74       | AH21 | I/O         | B4A_TX_B68_N                     | Bank4A           |

| 76       | AG21 | I/O         | B4A_TX_B65_P                     | Bank4A           |

| 78       | AF20 | I/O         | B4A_TX_B64_P                     | Bank4A           |

| 80       | AG20 | I/O         | B4A_TX_B64_N                     | Bank4A           |

| 82       | AG19 | I/O         | B4A_TX_B61_P                     | Bank4A           |

| 84       | AH19 | I/O         | B4A_TX_B61_N                     | Bank4A           |

| 86       | AG18 | I/O         | B4A_TX_B60_P                     | Bank4A           |

| 88       | AH18 | I/O         | B4A_TX_B60_N                     | Bank4A           |

| 90       | AF18 | I/O         | B4A_TX_B57_P                     | Bank4A           |

| 92       |      | PWR         | GND                              | Power            |

| 94       | AH17 | I/O         | B4A_TX_B56_P                     | Bank4A           |

| 96       | AH16 | I/O         | B4A_TX_B56_N                     | Bank4A           |

| 98       | AG15 | I/O         | B4A_TX_B53_P                     | Bank4A           |

| 100      | AH14 | I/O         | B4A_TX_B53_N                     | Bank4A           |

| 102      | AG14 | I/O         | B4A_TX_B52_P                     | Bank4A           |

| 104      | AH13 | I/O         | B4A_TX_B52_N                     | Bank4A           |

| 106      | AH12 | I/O         | B4A_TX_B49_P                     | Bank4A           |

| 108      |      | PWR         | GND                              | Power            |

| 110      | AG11 | I/O         | B4A_TX_B48_P                     | Bank4A           |

| 112      | AH11 | I/O         | B4A_TX_B48_N                     | Bank4A           |

| 114      | AG10 | I/O         | B4A_TX_B45_P                     | Bank4A           |

| 116      | AH9  | I/O         | B4A_TX_B45_N                     | Bank4A           |

| 118      | AG9  | I/O         | B4A_TX_B44_P                     | Bank4A           |

| 120      | AH8  | I/O         | B4A_TX_B44_N                     | Bank4A           |

| 122      | AG8  | I/O         | B4A_TX_B41_P                     | Bank4A           |

| 124      | AH7  | I/O         | B4A_TX_B41_N/RZQ0                | Bank4A           |

#### Table 9: Top Edge FPGA Bank4A I/O Pins

Table 10: Top Edge Key Missing Pins

| PIN | TYPE | SIGNAL | GROUP |

|-----|------|--------|-------|

| 126 | KEY  | —      |       |

| 128 | KEY  | —      |       |

| 130 | KEY  | —      |       |

| 132 | KEY  | —      |       |

Bank3B signals are another group of general FPGA I/O pins. These should be treated the same as the Bank4A pins. Additionally, there is a pair of connections that have dedicated clock routes to the Bottom Left Fractional PLL. If the fPLL external feedback is needed, or the CLKOUT from the fPLL, be sure to properly assign these resources.

| PIN | Ball | TYPE | SIGNAL                                         | GROUP  |

|-----|------|------|------------------------------------------------|--------|

| 134 |      | PWR  | +VIO_3B <sup>15</sup>                          | Power  |

| 136 |      | PWR  | GND                                            | Power  |

| 138 | AE8  | I/O  | B3B_TX_B29_P                                   | Bank3B |

| 140 | AF9  | I/O  | B3B_TX_B29_N                                   | Bank3B |

| 142 | AE7  | I/O  | B3B_TX_B28_P                                   | Bank3B |

| 144 | AF8  | I/O  | B3B_TX_B28_N                                   | Bank3B |

| 146 | AF5  | I/O  | B3B_TX_B32_P                                   | Bank3B |

| 148 | AF6  | I/O  | B3B_TX_B32_N                                   | Bank3B |

| 150 | AF7  | I/O  | B3B_TX_B33_P                                   | Bank3B |

| 152 | AG6  | I/O  | B3B_TX_B33_N                                   | Bank3B |

| 154 | AH6  | I/O  | B3B_TX_B40_P                                   | Bank3B |

| 156 | AH5  | I/O  | B3B_TX_B40_N                                   | Bank3B |

| 158 |      | PWR  | GND                                            | Power  |

| 160 | AG5  | I/O  | B3B_TX_B37_P/BL_CLKOUT0/BL_CLKOUT_P/FPLL_BL_FB | Bank3B |

| 162 | AH4  | I/O  | B3B_TX_B37_N/BL_CLKOUT1/BL_CLKOUT_N            | Bank3B |

| 164 | AE4  | I/O  | B3B_TX_B25_P                                   | Bank3B |

| 166 | AF4  | I/O  | B3B_TX_B25_N                                   | Bank3B |

| 168 | AH3  | I/O  | B3B_TX_B36_P                                   | Bank3B |

| 170 | AH2  | I/O  | B3B_TX_B36_N                                   | Bank3B |

| Table 11: Top Edge FPGA Bank3B I/O Pins |

|-----------------------------------------|

|-----------------------------------------|

Bank8A provides a few clock connection to the Top Left Fractional PLL. Note that there may be difficulty routing this clear across the FPGA to use with logic in the quadrants that include the Bank3 and Bank4 I/O pins.

|     |      |      | Table 12: Top Euge From Dalikon 1/0 Fills     |        |

|-----|------|------|-----------------------------------------------|--------|

| PIN | Ball | TYPE | SIGNAL                                        | GROUP  |

| 172 | E11  | I/O  | CLK6_P/FPLL_TL_FB_P/B8A_RX_T9_P               | Bank8A |

| 174 | D11  | I/O  | CLK6_N/FPLL_TL_FB_N/B8A_RX_T9_N               | Bank8A |

| 176 |      | PWR  | VIO_8A <sup>16</sup>                          | Power  |

| 178 | E8   | I/O  | TL_CLKOUT0/TL_CLKOUT_P/FPLL_TL_FB/B8A_TX_T4_P | Bank8A |

| 180 | D8   | I/O  | TL_CLKOUT1/TL_CLKOUT_N/B8A_TX_T4_N            | Bank8A |

| 182 |      | PWR  | GND                                           | Power  |

Table 12: Top Edge FPGA Bank8A I/O Pins

Before the high speed transceiver interface pins there is a group of reserved edge connector pins. These are reserved for a version of the module with expanded I/O connections replacing the FPGA DDR memory interface on the original MitySOM-5CSX. The FPGA DDR memory is connected to Banks 3A, 5A, and 5B. With the memory removed, there are pins available for most of the Bank3A and Bank5A connections. These pins also provide access to the fast parallel configuration options available in the Cyclone V. If these features are desired in an ed application, please contact Critical Link and inquire about availability.

$<sup>^{15}\</sup>mbox{The VREF3BN0}$  is half the externally supplied VIO\_3B voltage.

$<sup>^{16}\</sup>mbox{The VREF8AN0}$  is half the externally supplied VIO\_8A voltage.

| Table 13: Top Edge FPGA Bank3A Expanded I/O PINS |      |      |                         |           |  |

|--------------------------------------------------|------|------|-------------------------|-----------|--|

| PIN                                              | Ball | TYPE | SIGNAL 17               | GROUP     |  |

| 184                                              | AD5  | I/O  | NC,B3A_TX_B8_P          | NC,Bank3A |  |

| 186                                              | AE6  | I/O  | NC,B3A_TX_B8_N/PR_READY | NC,Bank3A |  |

| 188                                              | AC4  | I/O  | NC,B3A_TX_B6_P/DATA15   | NC,Bank3A |  |

| 190                                              | AD4  | I/O  | NC,B3A_TX_B6_N/DATA13   | NC,Bank3A |  |

| 192                                              | AA4  | I/O  | NC,B3A_TX_B4_P/DATA11   | NC,Bank3A |  |

| 194                                              | AB4  | I/O  | NC,B3A_TX_B4_N/DATA9    | NC,Bank3A |  |

| 196                                              | Y5   | I/O  | NC,B3A_TX_B2_P/DATA7    | NC,Bank3A |  |

| 198                                              | Y4   | I/O  | NC,B3A_TX_B2_N/DATA5    | NC,Bank3A |  |

Table 13: Top Edge FPGA Bank3A Expanded I/O Pins

The MitySOM-5CSX<sup>18</sup> includes 6 channels of high speed transceivers. These are available in groups of 3 transceivers and a reference clock. The receive pairs are available on the top edge of the module. The PCI Express Hard Controller can also be utilized through these transceivers. If using the PCIe interface, it is recommended to assign the channels starting with pair 0 along with the GXB\_REFCLK0 pair. The PCIe can be configured as an endpoint or a root port. As an endpoint, the Configuration via Protocol (CvP) can be utilized for the fastest configuration option.

| PIN | Ball | TYPE | SIGNAL 18        | GROUP   |

|-----|------|------|------------------|---------|

| 200 |      | PWR  | GND              | Power   |

| 202 | AF2  | Ι    | GXB_RX_0_P,NC    | GXB0,NC |

| 204 | AF1  | Ι    | GXB_RX_0_N,NC    | GXB0,NC |

| 206 |      | PWR  | GND              | Power   |

| 208 | AB2  | Ι    | GXB_RX_1_P,NC    | GXB0,NC |

| 210 | AB1  | Ι    | GXB_RX_1_N,NC    | GXB0,NC |

| 212 |      | PWR  | GND              | Power   |

| 214 | V2   | Ι    | GXB_RX_2_P,NC    | GXB0,NC |

| 216 | V1   | Ι    | GXB_RX_2_N,NC    | GXB0,NC |

| 218 |      | PWR  | GND              | Power   |

| 220 | V5   | Ι    | GXB_REFCLK0_P,NC | GXB0,NC |

| 222 | V4   | Ι    | GXB_REFCLK0_N,NC | GXB0,NC |

| 224 |      | PWR  | GND              | Power   |

| 226 | P2   | Ι    | GXB_RX_3_P,NC    | GXB1,NC |

| 228 | P1   | Ι    | GXB_RX_3_N,NC    | GXB1,NC |

| 230 |      | PWR  | GND              | Power   |

| 232 | K2   | Ι    | GXB_RX_4_P,NC    | GXB1,NC |

| 234 | K1   | Ι    | GXB_RX_4_N,NC    | GXB1,NC |

| 236 |      | PWR  | GND              | Power   |

| 238 | F2   | Ι    | GXB_RX_5_P,NC    | GXB1,NC |

| 240 | F1   | Ι    | GXB_RX_5_N,NC    | GXB1,NC |

Table 14: Top Edge High Speed Transceiver Pins

The last group of signals provide additional HPS peripheral connections. As shown in Table 15, the Bank7C peripherals are available here. These connections provide access to the SD/MMC peripheral

<sup>&</sup>lt;sup>17</sup>These pins are reserved for modules that include the FPGA DDR interface. They are available on modules with Expanded I/O. Some of the expanded I/O pins can also be used for a wide configuration interface.

$<sup>^{18}</sup>$ The MitySOM-5CSE does not include the high speed transceivers on the FPGA. The GXB\_RX pins should be pulled low through a 10K $\Omega$  resistor to ground as noted in the Quartus pin report for 5CSE support.

or the USB0 peripheral. The USB1 group of signals are assigned to the peripheral on Bank7D. The MitySOM includes a USB ULPI Phy, the TUSB1211A1 from Texas Instruments, and the USB interface is provided through the edge connector pins. This provides the USB interface while consuming the minimal amount of pins. This USB interface includes the connections necessary to run the USB port in host mode or on-the-go. To complete the interface, add the USB\_VBUS power switch as desired, the required bulk capacitance, ESD protection, and the USB connector.

| PIN | Ball | TYPE              | SIGNAL                           | GROUP  |

|-----|------|-------------------|----------------------------------|--------|

| 242 |      | $I^{PU}$          | USB1_FAULT_N                     | USB1   |

| 244 | B12  | I/O               | SDMMC_CLK_IN/USB0_CLK/HPS_GPIO44 | Bank7C |

| 246 |      | O <sup>PU</sup>   | USB1_PS_ON                       | USB1   |

| 248 | B6   | I/O               | SDMMC_D1/USB0_D3/HPS_GPIO39      | Bank7C |

| 250 | C13  | I/O               | SDMMC_D0/USB0_D2/HPS_GPIO38      | Bank7C |

| 252 | A5   | I/O               | SDMMC_PWREN/USB0_D1/HPS_GPIO37   | Bank7C |

| 254 | B8   | I/O               | SDMMC_CLK/USB0_STP/HPS_GPIO45    | Bank7C |

| 256 |      | 0                 | RTC_PSW/IRQ2_N <sup>19</sup>     | RTC    |

| 258 | D14  | I/O               | SDMMC_CMD/USB0_D0/HPS_GPIO36     | Bank7C |

| 260 | B9   | I/O               | SDMMC_D3/USB0_NXT/HPS_GPIO47     | Bank7C |

| 262 | B11  | I/O               | SDMMC_D2/USB0_DIR/HPS_GPIO46     | Bank7C |

| 264 | H13  | I/O               | SDMMC_D4/USB0_D4/HPS_GPIO40      | Bank7C |

| 266 | A4   | I/O               | SDMMC_D5/USB0_D5/HPS_GPIO41      | Bank7C |

| 268 | H12  | I/O               | SDMMC_D6/USB0_D6/HPS_GPIO42      | Bank7C |

| 270 | B4   | I/O               | SDMMC_D7/USB0_D7/HPS_GPIO43      | Bank7C |

| 272 |      | I/O               | USB1_ID                          | USB1   |

| 274 |      | I/O               | USB1_D_N                         | USB1   |

| 276 |      | I/O               | USB1_D_P                         | USB1   |

| 278 |      | PWR <sup>20</sup> | +USB1_VBUS <sup>21</sup>         | USB1   |

| 280 |      | PWR               | GND                              | Power  |

#### Table 15: Top Edge Bank7C and Bank7D Peripheral I/O Pins

#### 2.1.2 Bottom Edge Connector

On the bottom edge connector, the first group of signals include a mix of configuration signals and various reset/control signals. The MSEL pins define the FPGA configuration mode. Altera recommends tying the MSEL connections directly to power or ground. If configuring the FPGA from the HPS, set the MSEL to one of the FPPx16<sup>22</sup> configuration options. For many designs, this can simply be set to MSEL=00000. Note that there are 5 MSEL connections – one is on the top edge connector.

The Config group of pins provides the connections necessary to configure the FPGA from a prom. The MitySOM-5CSx Dev Board includes a footprint to solder in a prom to try this interface out. The expanded I/O versions of the MitySOM-5CSx support wider configuration interfaces.

$<sup>^{19}</sup>$ The RTC\_PSW/IRQ2\_N output is an output from the AB1805-T3 real-time clock. This can be used for a periodic power-up or other creative power saving modes. See 3.2 VCC Power Switched section of the Abracon AB1805-T3 datasheet for details of switched power.

$<sup>^{20}</sup>$ This net includes a 0.1uF cap. Add the bulk capacitance necessary to meet the USB specification for your device application. This will generally be 1uF to 100uF and is specific to the mode of operation for the USB endpoint.

$<sup>^{21}</sup>$  Connect a 1K $\Omega$  series resistor to +5V\_USB\_VBUS to avoid the danger of a possible connection to the adjacent GND pin. The module only needs to sample the USB1\_VBUS voltage for controlling the USB phy to support Ont-th-Go operation.

<sup>&</sup>lt;sup>22</sup>https://www.altera.com/en\_US/pdfs/literature/hb/cyclone-v/cv\_52007.pdf There are many configuration options for the Cyclone V such as the configuration mode, bitstream compression, design security. The details can be found in Altera's dosumentation.

| PIN | TYPE | SIGNAL | GROUP |

|-----|------|--------|-------|

| E1  | PWR  | RSVD   |       |

|     | GAP  | NC     |       |

|     | GAP  | NC     |       |

| E3  | PWR  | GND    | Power |

| E3  | PWR  | GND    | Power |

| E3  | PWR  | GND    | Power |

| E3  | PWR  | GND    | Power |

| E3  | PWR  | GND    | Power |

| E3  | PWR  | GND    | Power |

| E3  | PWR  | GND    | Power |

| E3  | PWR  | GND    | Power |

| E3  | PWR  | GND    | Power |

# Table 16: Bottom Edge Reserved [High] Power Pins

Table 17: Bottom Edge Main Power Pins

| PIN | TYPE | SIGNAL | GROUP |

|-----|------|--------|-------|

| 1   | PWR  | VIN+5V | Power |

| 3   | PWR  | VIN+5V | Power |

| 5   | PWR  | VIN+5V | Power |

| 7   | PWR  | VIN+5V | Power |

| 9   | PWR  | VIN+5V | Power |

| 11  | PWR  | GND    | Power |

| 13  | PWR  | GND    | Power |

| 15  | PWR  | GND    | Power |

| 17  | PWR  | GND    | Power |

Both reset connections are available on the edge connector: hard and soft reset; also known as cold and warm reset. The hard reset is the Power-On-Reset (POR) and is active low. The soft reset is labeled HPS\_RST\_N. These should be connected to an open collector output if driving the reset from the carrier board. The MitySOM module includes a  $10K\Omega$  pull-up resistor on each reset line. The lone Bank5A connection is here to provide the PCIe reset connection required to support CvP configuration. This signal is on a 1.35V bank, but can be pulled to +3.3V with a  $10K\Omega$  resistor. If not using this signal for the PCIe interface, it can be used as an additional FPGA I/O.

The Bank7A HPS\_CLK2 connection is available here as well. This can be used to run the HPS peripherals off a clock source other than the 25MHz included on the MitySOM. This is not required in many designs. Additionally, two pairs of connections are reserved here for Expanded I/O versions. On modules without Expanded I/O, these pins are not connected.

<sup>&</sup>lt;sup>23</sup>These signals are only available on the modules with expanded I/O; otherwise, they are not connected internal to the module.

| PIN | Ball | TYPE                 | SIGNAL                                    | GROUP     |

|-----|------|----------------------|-------------------------------------------|-----------|

| 19  | D20  | Ι                    | B7A_HPS_CLK2                              | Bank7A    |

| 21  | W15  | I/O                  | B5A_PERSTL1_N                             | Bank5A    |

| 23  | A23  | I/O <sup>PU10K</sup> | HPS_RST_N                                 | Reset     |

| 25  | H19  | I/O <sup>PU10K</sup> | HPS_POR_N                                 | Reset     |

| 27  | AA8  | I/O                  | PGM_FPGA_DCLK                             | Config    |

| 29  | J10  | Ι                    | B9A_MSEL0                                 | MSEL      |

| 31  | AB6  | I/O                  | PGM_FPGA_D3                               | Config    |

| 33  | AC5  | I/O                  | PGM_FPGA_D2                               | Config    |

| 35  | AC6  | I/O                  | PGM_FPGA_D1                               | Config    |

| 37  | AD7  | I/O                  | PGM_FPGA_D0                               | Config    |

| 39  | F7   | I/O <sup>PU10K</sup> | B9A_nCONFIG                               | Config    |

| 41  | H8   | I/O <sup>PU10K</sup> | B9A_nSTATUS                               | Config    |

| 43  | AA6  | I/O                  | PGM_FPGA_CSO_N                            | Config    |

| 45  | H9   | Ι                    | B9A_MSEL1                                 | MSEL      |

| 47  | AF26 | I/O                  | NC,B5A_TX_R1_P <sup>23</sup>              | NC,Bank5A |

| 49  | AE26 | I/O                  | NC,B5A_TX_R1_N/PR_REQUEST <sup>23</sup>   | NC,Bank5A |

| 51  | G6   | Ι                    | B9A_MSEL2                                 | MSEL      |

| 53  | AE25 | I/O                  | NC,B5A_TX_R3_P/nCEO <sup>23</sup>         | NC,Bank5A |

| 55  | AD26 | I/O                  | NC,B5A_TX_R3_N/CvP_CONFDONE <sup>23</sup> | NC,Bank5A |

| 57  | K10  | Ι                    | B9A_MSEL3                                 | MSEL      |

Table 18: Bottom Edge Config Group Pins

Table 19 shows the Bank4A connections available on the bottom edge connector. These are similar to the Bank4A connections on the top edge, but include receive SERDES Hard IP blocks. These can also be used as Emulated LVDS outputs and the signal names are assigned based on the 110KLE device connections. There are two clock input pairs in this group as well. The CLK2 pair is labeled CLK2DDR because the clock reference for the FPGA DDR interface should be brought in on this pair. This is necessary to meet timing for the FPGA DDR interface. If this clock source is a single ended signal, preference should be given to the CLK2DDR\_P input because this input pin has a dedicated input to the fPLL and will have the best jitter performance.

There is a key slot for edge connector alignment. Table 20 identifies the missing pins.

Two more Bank4A pairs are available after the key slot. Then there is a group of Bank3B pairs and a Bank8A pair. Two of the pairs in this group are clock inputs. CLK0 also has the external feedback connection for the Bottom Left fPLL.

| PIN | Ball | TYPE | SIGNAL                 | GROUP  |

|-----|------|------|------------------------|--------|

| 59  |      | PWR  | GND                    | Power  |

| 61  | AF25 | I/O  | B4A_RX_B78_P           | Bank4A |

| 63  | AG25 | I/O  | B4A_RX_B78_N           | Bank4A |

| 65  | AC22 | I/O  | B4A_RX_B75_P           | Bank4A |

| 67  | AC23 | I/O  | B4A_RX_B75_N           | Bank4A |

| 69  | AE24 | I/O  | B4A_RX_B74_P           | Bank4A |

| 71  | AE23 | I/O  | B4A_RX_B74_N           | Bank4A |

| 73  | AG23 | I/O  | B4A_RX_B70_P           | Bank4A |

| 75  | AF23 | I/O  | B4A_RX_B70_N           | Bank4A |

| 77  | AD23 | I/O  | B4A_RX_B67_P           | Bank4A |

| 79  | AE23 | I/O  | B4A_RX_B67_N           | Bank4A |

| 81  |      | PWR  | GND                    | Power  |

| 83  | AF22 | I/O  | B4A_RX_B66_P           | Bank4A |

| 85  | AF21 | I/O  | B4A_RX_B66_N           | Bank4A |

| 87  | AE20 | I/O  | B4A_RX_B62_P           | Bank4A |

| 89  | AD20 | I/O  | B4A_RX_B62_N           | Bank4A |

| 91  | AA19 | I/O  | B4A_RX_B59_P           | Bank4A |

| 93  | AA18 | I/O  | B4A_RX_B59_N           | Bank4A |

| 95  | AE19 | I/O  | B4A_RX_B58_P           | Bank4A |

| 97  | AD19 | I/O  | B4A_RX_B58_N           | Bank4A |

| 99  | Y15  | I/O  | B4A_RX_B55_P/CLK3_P    | Bank4A |

| 101 | AA15 | I/O  | B4A_RX_B55_N/CLK3_N    | Bank4A |

| 103 |      | PWR  | GND                    | Power  |

| 105 | AD17 | I/O  | B4A_RX_B54_P           | Bank4A |

| 107 | AE17 | I/O  | B4A_RX_B54_N           | Bank4A |

| 109 | W14  | I/O  | B4A_RX_B51_P           | Bank4A |

| 111 | V13  | I/O  | B4A_RX_B51_N           | Bank4A |

| 113 | AF17 | I/O  | B4A_RX_B50_P           | Bank4A |

| 115 | AG16 | I/O  | B4A_RX_B50_N           | Bank4A |

| 117 | Y13  | I/O  | CLK2DDR_P/B4A_RX_B47_P | Bank4A |

| 119 | AA13 | I/O  | CLK2DDR_N/B4A_RX_B47_N | Bank4A |

| 121 | AF15 | I/O  | B4A_RX_B46_P           | Bank4A |

| 123 | AE15 | I/O  | B4A_RX_B46_N           | Bank4A |

| 125 |      | PWR  | GND                    | Power  |

# Table 19: Bottom Edge Bank4A I/O Pins PIN Ball TYPE SIGNAL

Table 20: Bottom Edge Key Missing Pins

| PIN | TYPE | SIGNAL | GROUP |

|-----|------|--------|-------|

| 127 | KEY  | —      |       |

| 129 | KEY  | —      |       |

| 131 | KEY  | —      |       |

| PIN | Ball | TYPE | SIGNAL                           | GROUP  |

|-----|------|------|----------------------------------|--------|

| 133 | U14  | I/O  | B4A_RX_B43_P                     | Bank4A |

| 135 | U13  | I/O  | B4A_RX_B43_N                     | Bank4A |

| 137 | AG13 | I/O  | B4A_RX_B42_P                     | Bank4A |

| 139 | AF13 | I/O  | B4A_RX_B42_N                     | Bank4A |

| 141 | AE12 | I/O  | B3B_RX_B38_P                     | Bank3B |

| 143 | AD12 | I/O  | B3B_RX_B38_N                     | Bank3B |

| 145 | AD11 | I/O  | B3B_RX_B30_P                     | Bank3B |

| 147 | AE11 | I/O  | B3B_RX_B30_N                     | Bank3B |

| 149 | AF11 | I/O  | B3B_RX_B34_P                     | Bank3B |

| 151 | AF10 | I/O  | B3B_RX_B34_N                     | Bank3B |

| 153 |      | PWR  | GND                              | Power  |

| 155 | T13  | I/O  | B3B_RX_B35_P                     | Bank3B |

| 157 | T12  | I/O  | B3B_RX_B35_N                     | Bank3B |

| 159 | T11  | I/O  | B3B_RX_B27_P                     | Bank3B |

| 161 | U11  | I/O  | B3B_RX_B27_N                     | Bank3B |

| 163 | V12  | I/O  | B3B_RX_B39_P                     | Bank3B |

| 165 | W12  | I/O  | B3B_RX_B39_N                     | Bank3B |

| 167 | V11  | I/O  | B3B_RX_B31_P/CLK0_P/FPLL_BL_FB_P | Bank3B |

| 169 | W11  | I/O  | B3B_RX_B31_N/CLK0_N/FPLL_BL_FB_N | Bank3B |

| 171 | AD10 | I/O  | B3B_RX_B26_P                     | Bank3B |

| 173 | AE9  | I/O  | B3B_RX_B26_N                     | Bank3B |

| 175 |      | PWR  | GND                              | Power  |

| 177 | D12  | I/O  | B8A_RX_T1_P/CLK7_P               | Bank8A |

| 179 | C12  | I/O  | B8A_RX_T1_N/CLK7_N               | Bank8A |

On the bottom, there is another group of reserved edge connector pins before the high speed transceiver connections. Table 22 has the details of these Expanded I/O connections. On the expanded I/O version of the module, there is an additional VIO power input to power the FPGA banks consumed by the FPGA DDR memory interface on the original module. This is currently a no-connect. Carrier board designs that expect to migrate to the smaller MitySOM-5CSE device should provide power to this pin.

|     | Tuble 22. Dottom Luge Data of the Lapanaed for this |      |                |              |  |  |

|-----|-----------------------------------------------------|------|----------------|--------------|--|--|

| PIN | Ball                                                | TYPE | SIGNAL         | GROUP        |  |  |

| 181 |                                                     | PWR  | NC,+VIO_3A5A5B | Expanded I/O |  |  |

| 183 | AA20                                                | I/O  | NC,B5A_RX_R2_P | NC,Bank5A    |  |  |

| 185 | Y19                                                 | I/O  | NC,B5A_RX_R2_N | NC,Bank5A    |  |  |

| 187 | Y17                                                 | I/O  | NC,B5A_RX_R4_P | NC,Bank5A    |  |  |

| 189 | Y18                                                 | I/O  | NC,B5A_RX_R4_N | NC,Bank5A    |  |  |

| 191 | Y11                                                 | I/O  | NC,B3A_RX_B7_P | NC,Bank3A    |  |  |

| 193 | AA11                                                | I/O  | NC,B3A_RX_B7_N | NC,Bank3A    |  |  |

| 195 | U10                                                 | I/O  | NC,B3A_RX_B5_P | NC,Bank3A    |  |  |

| 197 | V10                                                 | I/O  | NC,B3A_RX_B5_N | NC,Bank3A    |  |  |

| 199 | U9                                                  | I/O  | NC,B3A_RX_B3_P | NC,Bank3A    |  |  |

| 201 | T8                                                  | I/O  | NC,B3A_RX_B3_N | NC,Bank3A    |  |  |

| 203 | W8                                                  | I/O  | NC,B3A_RX_B1_P | NC,Bank3A    |  |  |

| 205 | Y8                                                  | I/O  | NC,B3A_RX_B1_N | NC,Bank3A    |  |  |

#### Table 22: Bottom Edge Bank5A/3A Expanded I/O Pins

The transmit interfaces of the high speed transceivers are available on the bottom edge connector along with the second reference clock input. These connections are detailed in Table 23.

| PIN | Ball | TYPE | SIGNAL        | GROUP |

|-----|------|------|---------------|-------|

| 207 |      | PWR  | GND           | Power |

| 209 | AD2  | 0    | GXB_TX_0_P    | GXB0  |

| 211 | AD1  | 0    | GXB_TX_0_N    | GXB0  |

| 213 |      | PWR  | GND           | Power |

| 215 | Y2   | 0    | GXB_TX_1_P    | GXB0  |

| 217 | Y1   | 0    | GXB_TX_1_N    | GXB0  |

| 219 |      | PWR  | GND           | Power |

| 221 | T2   | 0    | GXB_TX_2_P    | GXB0  |

| 223 | T1   | 0    | GXB_TX_2_N    | GXB0  |

| 225 |      | PWR  | GND           | Power |

| 227 | P8   | Ι    | GXB_REFCLK1_P | GXB1  |

| 229 | N8   | Ι    | GXB_REFCLK1_N | GXB1  |

| 231 |      | PWR  | GND           | Power |

| 233 | M2   | 0    | GXB_TX_3_P    | GXB1  |

| 235 | M1   | 0    | GXB_TX_3_N    | GXB1  |

| 237 |      | PWR  | GND           | Power |

| 239 | H2   | 0    | GXB_TX_4_P    | GXB1  |

| 241 | H1   | 0    | GXB_TX_4_N    | GXB1  |

| 243 |      | PWR  | GND           | Power |

| 245 | D2   | 0    | GXB_TX_5_P    | GXB1  |

| 247 | D1   | 0    | GXB_TX_5_N    | GXB1  |

|           |         | _    | _    | _     |                  |

|-----------|---------|------|------|-------|------------------|

| Table 22  | Dottom  | Edaa | Lich | Crood | Tropooirron Ding |

| Table Zor | DOLLOIN | гаае |      | Speed | Transceiver Pins |

|           |         |      |      |       |                  |

The last group of signals are the connections to Bank7B. These connections could be an RGMII Ethernet phy interface, an interface to NAND or more GPIO connections. The I/O voltage rail power for this interface is provided by the MitySOM and is +1.8V. This I/O voltage was chosen to save some power. Unfortunately, this limits the available NAND densities available as well as the maximum size of the QSPI device on the MitySOM. If an application requires much larger flash memory, please contact Critical Link to discuss the application.

| PIN | Ball | TYPE               | SIGNAL                                                | GROUP       |

|-----|------|--------------------|-------------------------------------------------------|-------------|

| 249 |      | PWR                | RES_BOOTSEL1 <sup>24</sup>                            | BSEL        |

| 251 | J12  | I/O                | RGMII1_RX_CLK/NAND_DQ5/HPS_GPIO24                     | Bank7B      |

| 253 | D15  | I/O                | HPS_GPIO28,BOOTSEL2/NAND_WE                           | Bank7B,BSEL |

| 255 | J13  | I/O                | RGMII1_RX_CTL/NAND_DQ3/HPS_GPIO22                     | Bank7B      |

| 257 | A14  | I/O                | RGMII1_RXD0/NAND_DQ0/HPS_GPIO19                       | Bank7B      |

| 259 | A11  | I/O                | RGMII1_RXD1/NAND_DQ6/HPS_GPIO25                       | Bank7B      |

| 261 | C15  | I/O                | RGMII1_RXD2/NAND_DQ7/HPS_GPIO26                       | Bank7B      |

| 263 | A9   | I/O                | RGMII1_RXD3/NAND_WP/HPS_GPIO27                        | Bank7B      |

| 265 | A13  | I/O                | RGMII1_MDC/NAND_DQ2/I <sup>2</sup> C3_SCL/HPS_GPIO21  | Bank7B      |

| 267 | E16  | I/O                | RGMII1_MDIO/NAND_DQ1/I <sup>2</sup> C3_SDA/HPS_GPIO20 | Bank7B      |

| 269 | A12  | I/O                | RGMII1_TX_CTL/NAND_DQ4/HPS_GPIO23                     | Bank7B      |

| 271 | J15  | I/O                | RGMII1_TX_CLK/NAND_ALE/HPS_GPIO14                     | Bank7B      |

| 273 |      | PWR <sub>OUT</sub> | VIO_7B7D_+1.8V <sup>25</sup>                          | Power       |

| 275 | D17  | I/O                | RGMII1_TXD3/NAND_RB/HPS_GPIO18                        | Bank7B      |

| 277 | A15  | I/O                | RGMII1_TXD2/NAND_RE/HPS_GPIO17                        | Bank7B      |

| 279 | J14  | I/O                | RGMII1_TXD1/NAND_CLE/HPS_GPIO16                       | Bank7B      |

| 281 | A16  | I/O                | RGMII1_TXD0/NAND_CE/HPS_GPIO15                        | Bank7B      |

#### Table 24: Bottom Edge Bank7B I/O Pins

$<sup>^{24}</sup>$ BOOTSEL1 is used locally on the SOM for the QSPI\_SS0 select line. It is available to the edge connector after a 10K $\Omega$  series resistor. Pull this pin high to VIO\_7B7D\_+1.8V or low to GND to define BSEL1.

$<sup>^{25}</sup>$ The voltage rail for HPS Bank7B and Bank7D is generated by the SOM. The standard products use a +1.8V I/O rail for these banks to conserve power. If using Bank7B connections, the I/O voltage for the RGMII Phy or NAND device can be driven by the power supply output from the module.

# 2.2 Module Reset

Both reset connections are available on the edge connector. The Power-On-Reset, or Cold reset is asserted active-low at power-on until all the monitored power supply rails are alive. Note that this include the  $V_{CCBAT}$  connection and the device will not come out of reset without this supply powered up.

The Warm reset is also available as a less severe reset signal. Consult the Altera documentation for the differences between the two reset signals. Note that both resets are active-low and can be read or driven by the MitySOM. These should be driven by an open-collector output and pull-up resistors are included on the module, so they are not necessary on the carrier board.

# 2.3 JTAG / TRACE

The JTAG connections are routed to a debug header on the MitySOM-5CSx. These can be accessed through a simple JTAG breakout board available in the MitySOM-5CSx Dev Kits or using a MitySOM-5CSx JTAG/TRACE high speed debug adapter. The TRACE interface can be routed to the debug header on the SOM instead of the edge connector for a high-bandwidth trace interface. This requires additional ARM debug hardware to take advantage of, but the debug adapter also includes the BlasterII interface for high speed debug.

# 2.4 Module Boot Configuration

Boot options are defined by three sets of inputs: MSEL, BSEL, and CSEL. MSEL defines the FPGA configuration scheme. BSEL identifies the boot device to try first for the HPS. Note that the HPS will try additional boot sources if the boot selection initially fails. CSEL is the clock selection and defined the clock divisors to use after reset.

Defining the desired FPGA configuration mode is is done through the MSEL input pins. These are dedicated inputs that need to be connected to power or ground with low impedance paths. Additionally, they need to be valid at power-on and the high state cannot be gated by the I/O power enable.

The BSEL inputs are multi-function pins. At reset, they are read to determine the desired boot device. After reset, they are used for other I/O functions. These should be pulled high or low through 1K $\Omega$  or higher resistors. The BSEL nets are in the power domains of their respective Banks in the FPGA. BSEL0 is in Bank7A and powered by +3.3V (VIH > 2.1V). The other two, BSEL1 and BSEL2 are in Bank7B powered by 1.8V. The 1.8V is provided by the SOM for IO power, such as used on the RGMII Ethernet interface. If you want to pull these to +3.3V, that is OK as long as you limit the current to below 8 or 10 mA worst case. Pull-up / pull-down values of 1K $\Omega$  and 10K $\Omega$  are very safe. BSEL1 has a 10K $\Omega$  series resistor making it safe to tie directly high or low – even if high is +3.3V. This signal is used for QSPI\_SSO after reset on the SOM itself and the 10K $\Omega$  makes sure there is isolation for running the QSPI interface. The series resistor does not impact the pull-up/pull-down as minimal current is pulled, so the same resistor scheme can be used.

Lastly, the CSEL inputs define the clock scheme coming out of reset. These are also multi-function pins, read during reset and other Bank7A I/O pins after reset. Being in Bank7A, their power domain is +3.3V. Add a pull-up or pull-down resistor to define the desired clock option.

Altera has identified an errata with the HPS PLL where it will sometimes fail to lock at reset. When this happens the HPS may hang during the BootROM stage and fail to proceed to the Preloader, or it may fail SDRAM calibration during the Preloader. To avoid this errata, follow the workaround provided

by  $Altera^{26}$ . This includes setting the CSEL to 00 to bypass the PLL at reset and apply the patch to the Preloader.

See Altera's Booting and Configuration guide for more information<sup>27</sup>.

# **3** Electrical Requirements

# **3.1 Power Supplies**

The module takes 5V power in and generates all the supply rails required for the FPGA core and HPS peripherals. The I/O Voltages have been exposed to the edge connector to support the wide range of I/O standards that are available.

# 3.2 Power Sequencing

The Cyclone V supports any power sequence, but there is some benefit in sequencing the module power followed by the VIO power supplies. To support this sequencing, there is a VIO-ENABLE signal on the edge connector that indicates when the core voltages and aux supplies are up. Once this signal is high, the VIO supplies should be enabled to complete the power-up sequence.

### 3.3 I/O Interfaces

| Symbol             | Description                       | Minimum    | Typical    | Maximum | Unit |

|--------------------|-----------------------------------|------------|------------|---------|------|

| V <sub>IN</sub>    | Module Input Voltage              | 4.85       | 5.0        | 5.15    | V    |

| I <sub>IN</sub>    | Module Input Current              | _          | _          | 2.5     | Α    |

|                    | 5CSX-H6-42A                       |            |            | ~2      | Α    |

|                    | 5CSE-L2-3XA                       |            |            | ~1      | Α    |

|                    | 5CSX-H6-53B                       | —          | _          | ~2      | Α    |

| V <sub>CCPD</sub>  | I/O pre-driver (VIO $> 2.5V$ )    | 2.85       | 3.0 or 3.3 | VIO     | V    |

|                    | I/O pre-driver (VIO $\leq 2.5$ V) | —          | 2.5        | —       |      |

| V <sub>CCIO</sub>  | I/O buffers (1.2-3.3V)            | 1.14       | 1.2 to 3.3 | 3.465   | V    |

| V <sub>CCBAT</sub> | Battery back-up power supply      | $1.2^{28}$ | —          | 3.0     | V    |

|                    | (For design security key and RTC) |            |            |         |      |

| VI                 | I/O Pin DC Input Voltage          | -0.5       | —          | 3.6     | V    |

| Vo                 | Output Voltage                    | 0          | —          | VIO     | V    |

|                    | Operating Junction Temperature    |            |            |         |      |

| T <sub>J</sub>     | (CT)                              | 0          |            | 85      | °C   |

|                    | (IT)                              | -40        | —          | 100     | °C   |

|                    | (AT)                              | -40        | —          | 125     | °C   |

| t <sub>RAMP</sub>  | Power Supply Ramp Time            | 0.2        |            | 4       | ms   |

<sup>26</sup>http://www.altera.com/support/kdb/solutions/rd06202014\_496.html

$^{27}$ http://www.altera.com/content/dam/altera-www/global/en\_US/pdfs/literature/hb/cyclone-v/cv\_5400A.pdf  $^{28}$ At V<sub>CCBAT</sub> of 1.2V to 1.5V, the minimum JTAG TCK clock period is extended to 167 ns. See  $cv_51002$  for details.

# 3.4 I/O Protection

- Limit Bank connections to the Bank's I/O Voltage.

- Connect a  $1K\Omega$  series resistor to  $+5V\_USB\_VBUS$  to avoid the danger of any possible connection to the adjacent GND. The module only needs to sample the voltage for controlling the USB phy.

# 3.5 Battery Backup

There is a very low power RTC on the MitySOM module. The +3VBAT input provides the battery backup power for the RTC along with the VBAT connection on the Cyclone V. If a battery is not used, connect this line to +2.5V or +3V. The recommended electrical range for the battery has a maximum of +3.0V, but the absolute max spec is 3.9V.

# 4 Mechanical Requirements

# 4.1 Module Connectors

The MitySOM-5CSx uses the physical MXM 3.0 standard edge connector for the module I/Os. The recommended initial connector is *MM70-314-310B1-1-R300* from JAE Electronics. Other standard MXM 3.0 connectors are expected to be compatible. If using another connector, ensure the pins at the opposite end of the main ganged power input (pins E1, E2, E3 and E4) are individual pins. According to the MXM specification, the top edge connector row has the two end pins tied together. However, on the MitySOM, these are two separate pins. If they are ganged and the recommended series resistor is included, the USB1 interface will not power up, but otherwise should cause no damage.

# 4.2 Mounting Methods

The MXM connector has no latch arms for retaining the module. Instead, there are two corner mounting holes for securing the module. This provides a secure means of fastening the module in an embedded design for reliable performance.

# 4.3 Shock & Vibration

This section will be filled in with additional shock and vibration test data.

# **5** General Design Guidelines

http://www.altera.com/content/dam/altera-www/global/en\_US/pdfs/literature/hb/cyclone-v/ cv\_51001.pdf "Cyclone V Device Overview"

|            | Table 25: FPGA Bank Pin Allocations |           |          |           |  |  |

|------------|-------------------------------------|-----------|----------|-----------|--|--|

|            | Bank                                | FPGA DDR  | Exp I/O  | Exp I/O   |  |  |

|            | Package U23                         | U672      | U672     | U672      |  |  |

|            | Fabric Size                         | 85/110kLE | 25/40kLe | 85/110kLe |  |  |

|            | 3A-FPGA DDR                         | 15        | -        | -         |  |  |

|            | 3A-Edge Pins                        | 1         | 16       | 16        |  |  |

| FPGA       | 3B                                  | 32        | 32       | 32        |  |  |

| I/O Bank   | 4A                                  | 68        | 68       | 68        |  |  |

|            | 5A-FPGA DDR                         | 16        | _        | _         |  |  |

|            | 5A-Edge Pins                        | -         | 16       | 16        |  |  |

|            | 5B-FPGA DDR                         | 7         | GND      | _         |  |  |

|            | 5B-Edge Pins                        | -         | GND      | _         |  |  |

| HPS Row    | 6A                                  | 56        | 56       | 56        |  |  |

| I/O Bank   | 6B                                  | 44        | 44       | 44        |  |  |

|            | 7A                                  | 19        | 19       | 19        |  |  |

| HPS Column | 7B                                  | 22        | 22       | 22        |  |  |

| I/O Bank   | 7C                                  | 12        | 12       | 12        |  |  |

|            | 7D                                  | 14        | 14       | 14        |  |  |

| FPGA       | 8A                                  | 6         | 6        | 6         |  |  |

| I/O Bank   | 8A-Grounded IOs                     | N/A       | 7⇒GND    | N/A       |  |  |

|            | Total                               | 312       | 305      | 305       |  |  |

### 5.1 **Pin Allocation**

#### 5.1.1 HPS Peripherals

• TRACE MUX

### 5.2 FPGA Size Migration Guide

The family of MitySOM-5CSx modules was designed to be pin compatible. As a design migrates between different modules within the MitySOM-5CSx family, there are some interfaces that are no longer available. There are also a few pins that become ground pins due to the U672 FPGA package pin migration limitations.

#### 5.2.1 High Speed Transceivers (GXB)

The first major option is whether or not the high speed transceivers (GXB) are included on the module. The models that include the GXB interfaces have model numbers starting with 5CSX, and the 5CSE models do not include the GXB interfaces.

Altera recommends connecting the GXB interface inputs to GND through  $10k\Omega$  resistors. This keeps the inputs safe, quiet and can save some power as well.

#### 5.2.2 FPGA DDR or Expanded I/O

The next feature selects either FPGA DDR or Expanded I/O edge connections. The FPGA DDR is a DDR3 memory connected to Banks 3A/5A/5B FPGA fabric I/O pins. The Bank 5B I/O pins are not available on the smaller 25kLE and 40kLE FPGA size devices, so FPGA DDR is only supported on the large device models with 85kLE or 110kLE FPGAs.

When the FPGA DDR memory feature is removed, it can be replaced by Expanded I/O connections to the edge connector. The Expanded I/O feature makes an additional 26 pins available from Banks 3A and 5A. See Section subsection 6.8 for details on the additional edge connections available with Expanded I/O. The additional pins also make it possible to use some of the advanced configuration options with the module, such as partial reconfiguration and the wide x16 configuration interface.

With the Expanded I/O feature, there is an additional VIO power connection to define the I/O voltage used by the additional FPGA Bank 3A and 5A pins. Make sure the power is supplied on the additional VIO\_3A5A5B edge connector pin. The modules without the Expanded I/Os have no connection to this pin to provide safe migration across the MitySOM-5CSx family modules.

#### 5.2.3 Bank5B and Bank8A Pins

If planning to migrate between small and large FPGA size options, beware of the 7 Bank5B pins that become ground on the 25kLE and 40kLE FPGA sizes. These pins are only used by the FPGA DDR memory option, as available on some large FPGA, 85kLE or 110kLE, modules. The Expanded I/O connections avoid these pins. Also note that on small FPGA, 25kLE and 40kLE, modules there are 7 Bank8A pins that are I/O pins instead of the ground pins they are on the large FPGA package. These pins must not be used as outputs; they are connected directly to ground on the MitySOM module. See Table 26 for the pin details.

| Table 26: Expanded I/O Ground Pins |      |             |                           |  |  |

|------------------------------------|------|-------------|---------------------------|--|--|