THE LOW-COST PROGRAMMABLE SILICON FOUNDATION FOR TARGETED DESIGN PLATFORMS

# BALANCING COST, SPACE, POWER AND PERFORMANCE

### $\Sigma$ The Programmable Imperative

- System designers in today's pricesensitive markets face a confluence of economic, financial, and market pressures

- Market windows are narrowing, design complexity is increasing, and product lifetimes are shrinking

- Developers need to do more with less and still push the limits of innovation to remain competitive

### $\Sigma$ Targeted Design Platforms

- Targeted Design Platforms from Xilinx and its network of third parties provide system designers with simpler and smarter methodologies for creating FPGA-based system-on-chip solutions

- Targeted Design Platforms enable software and hardware designers to leverage open standards, common design methodologies, development tools, and run-time platforms

- Designers can spend less time developing the infrastructure of an application and more time building differentiating features into their products

# Where Low Cost, Low Power Converge with High Performance

When design requirements call for low cost and low power, the new Spartan<sup>®</sup>-6 family is the answer. This silicon foundation of the Xilinx Targeted Design Platform merges industryleading process and programmable logic technology with transceiver capabilities and controllers for advanced memory support to deliver a high-performance FPGA for costsensitive applications. Innovation in advanced power management technology and the ability to operate at a lower power 1.0V core option enable the new Spartan-6 FPGA family to achieve 65% lower power than previous Spartan families.

### At the Heart of Innovation

The sixth generation in the Spartan FPGA Series enables system developers to meet demands for new features, while at the same time reducing system costs by up to half for lower-power, "greener" products. Supporting applications such as automotive infotainment, flat-panel displays, multi-function printers, set-top boxes, home networking, and video surveillance, Spartan-6 FPGAs offer an optimal balance of low risk, low cost, low power, and high performance.

# A Proven, Industry-Leading Architecture

The Spartan-6 FPGA family's efficient, dual-register six-input LUT logic structure leverages the industry's leading Virtex<sup>®</sup> architecture to enable cross-platform compatibility and to increase system performance. The addition of Virtex-series system-level blocks including DSP slices, high-speed transceivers, and PCI Express<sup>®</sup> endpoint block make for greater system-level integration than ever before.

# Spartan-6 FPGA Families

The Spartan<sup>®</sup>-6 FPGA family comprises of two domain-optimized sub-families with a mix of features matched to stringent market requirements for price-sensitive, high-volume applications:

**Spartan-6 LX FPGAs** are optimized for applications that require the absolute lowest cost. They support up to 147K logic cell density, 4.8Mb memory, integrated memory controllers, DSP slices, ease-ofuse, and high-performance Hard IP with an innovative open standards-based configuration. **Spartan-6 LXT FPGAs** extend the LX family to deliver up to eight 3.2Gbps GTP transceivers and an integrated PCI Express Block, both derived from proven Virtex<sup>®</sup> FPGA family technology, to provide the industry's lowest-risk and lowest-cost solution for serial connectivity. Discover how this new family delivers even higher performance, lower power, and lower system cost than previousgeneration Spartan FPGAs.

# Key Capability Overview

#### Greater Ease-of-Use

- Faster design using integrated wizards for built-in blocks, an efficient logic architecture derived from the Virtex series as well as development kits complete with IP and reference designs

- Easier configuration with broad, low-cost third-party flash support, and simplified two-pin auto-detect configuration

### New Levels of Performance

- Abundant logic resources with increased logic capacity of up to 147K logic cells enables driving high performance in systems

- Build high-performance digital signal processing systems for video, wireless, and many other applications with efficient, second-generation DSP48A1

- Simplify high-bandwidth interfaces with multi-voltage, multi-standard highperformance SelectIO<sup>™</sup> banks with 3.3V capability, an integrated memory controller block, and DisplayPort-enabled 3.2Gb/s GTP transceivers

- Integrated memory controller blocks enable streamlined access to video and data storage in external DDR3 memory, while double the block RAM provides a wider range of granularity (1x18Kb or 2x9Kb)

- Speedy embedded processing with enhanced MicroBlaze<sup>™</sup> soft processor

#### Faster, More Comprehensive Connectivity

- Connect to more with support for major single and double differential I/O standards

- Connect faster with 1Gbps differential I/O, multiple 3.2Gbps integrated serial transceivers, and 12.8Gbps memory bandwidth access

- Connect at lower cost with integrated SDRAM memory controller and PCI Express<sup>®</sup> interfaces

#### Twice the Capability, Half the Power

- Process more, faster with increased block RAM, 2X logic capability, 50% more DSP48A1 slices, six-input LUT with dual flip-flops, low noise, and flexible clocking

- Reduce power consumption with ~50%

lower dynamic power and ~40% lower

static power compared to previous

generation, and by using system-level power

management features

- 45nm process technology optimized for lowcost, cost-optimized wire-bond packaging and new hard IP blocks reduce size to help you drive down system costs

#### FEATURES OVERVIEW

| <b>45nm Low Power Process Technology</b><br>Optimized for cost, power and performance,<br>most efficient utilization of low-power copper<br>process technology | <ul> <li>Efficient six-input LUTs improve performance and minimize power</li> <li>LUT designed with dual flip-flops for pipelined applications</li> <li>Flexible LUTs are configurable as logic, distributed RAM, or shift registers</li> <li>From 3,800 to 147,000 logic cells for system-level integration</li> </ul>                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Low Cost by Design<br>Cost-optimized Virtex <sup>®</sup> -series based architecture                                                                            | <ul> <li>Multiple efficient integrated blocks</li> <li>Optimized selection of I/O standards</li> <li>Staggered I/O pads</li> <li>High-volume plastic wire-bonded packages</li> <li>Low-cost third-party configuration</li> </ul>                                                                                                                                                                                          |

| <b>1050MHz Clocking Technology</b><br>Clock Management Tile (CMT) for enhanced<br>performance                                                                  | <ul> <li>Low noise, flexible clocking</li> <li>Digital Clock Managers (DCMs) eliminate clock skew and duty cycle distortion</li> <li>Phase-Locked Loops (PLLs) for low-jitter clocking</li> <li>Frequency synthesis with simultaneous multiplication, division, and phase shifting</li> <li>Sixteen low-skew global clock networks</li> </ul>                                                                             |

| Increased Memory Block Capacity to 4.8Mbits<br>Block RAM with a wide range of granularity                                                                      | <ul> <li>Efficient block RAM</li> <li>Fast block RAM with byte write enable</li> <li>18Kb blocks can be split into two independent 9Kb block RAMs</li> </ul>                                                                                                                                                                                                                                                              |

| Integrated Memory Controllers<br>Only low-cost FPGA with integrated memory<br>controller blocks                                                                | <ul> <li>DDR, DDR2, DDR3, and LPDDR support</li> <li>Data rates up to 800Mbps (12.8Gbps peak bandwidth)</li> <li>Multi-port bus structure with independent FIFO to reduce design timing issues</li> <li>Simplifies memory interface and board layout</li> <li>Predictable timing for memory interface designs</li> <li>Software wizard to guide through the entire process</li> </ul>                                     |

| SelectIO <sup>™</sup> Interface Technology<br>Multi-voltage, multi-standard SelectIO banks                                                                     | <ul> <li>Up to 1,050Mbps data transfer rate per differential I/O</li> <li>Selectable output drive, up to 24mA per pin</li> <li>3.3V to 1.2V I/O standards and protocols</li> <li>Low-cost HSTL and SSTL memory interfaces</li> <li>Hot-swap compliance</li> <li>Adjustable I/O slew rates to improve signal integrity</li> </ul>                                                                                          |

| Up to 180 Efficient DSP48A1 Slices<br>Drive high-performance arithmetic and signal<br>processing                                                               | <ul> <li>Each slice contains a fast 18 x 18 multiplier and a 48-bit accumulator capable of operating at 250MHz</li> <li>Pipelining and cascading capability</li> <li>Pre-adder to assist in symmetric filter applications</li> </ul>                                                                                                                                                                                      |

| Enhanced Configuration and<br>Bitstream Protection<br>Reduce system cost, increase reliability, and<br>safeguard your design                                   | <ul> <li>Simplified configuration, supports low-cost standards</li> <li>Broad third-party SPI (up to x4) and NOR Flash support</li> <li>Feature-rich Xilinx Platform Flash with JTAG</li> <li>MultiBoot support for remote upgrade with multiple bitstreams, using watchdog protection</li> <li>Unique Device DNA identifier for design authentication</li> <li>AES bitstream encryption in the larger devices</li> </ul> |

| GTP Transceivers in Spartan-6 LXT: 100Mbps<br>to 3.2Gbps<br>Implement serial protocols at lowest power                                                         | <ul> <li>Up to 3.2Gbps performance</li> <li>High-speed interfaces: Serial ATA, Aurora, 1G Ethernet, PCI Express<sup>®</sup>, OBSAI, CPRI, EPON, GPON, DisplayPort, and XAUI</li> <li>Low power consumption: &lt; 150 mW (typical) at 3.2Gbps</li> </ul>                                                                                                                                                                   |

| PCI Express Block in Spartan-6 LXT FPGA<br>Integrated block for PCI Express designs                                                                            | <ul> <li>Works with GTP transceivers to deliver PCIe endpoint functionality</li> <li>Built-in hard IP frees user logic resources and reduces power</li> <li>PCI SIG-verified Gen1 compliance (on integrators list)</li> </ul>                                                                                                                                                                                             |

| Optimized Power Saving Modes<br>Hibernate power-down mode for zero power                                                                                       | <ul> <li>Suspend mode maintains state and configuration with multi-pin wake-up, control enhancement</li> <li>Software power optimization option</li> </ul>                                                                                                                                                                                                                                                                |

| Embedded Processing<br>Faster embedded processing with enhanced,<br>low-cost, MicroBlaze™ soft processor                                                       | <ul> <li>New MicroBlaze 7.0 adds MMU and FPU for greater functionality</li> <li>Six-input LUT architecture improves performance and efficiency for comparator and multiplexer</li> <li>2X flip-flops for embedded registers</li> <li>Hard DRAM memory controller with 12.8Gbps memory bandwidth</li> </ul>                                                                                                                |

# How Targeted Design Platforms accelerate innovation

## **Automotive Infotainment**

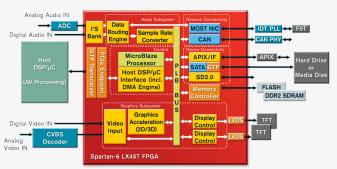

#### In-Car Infotainment System

Serving as a companion to the host processor, a single Spartan-6 LX45T FPGA supports audio/ video acceleration, graphics subsystem, and vehicle networking functions.

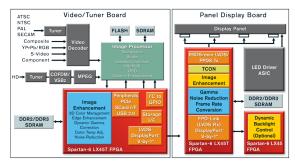

# Flat-Panel Displays

#### High-Resolution Video Flat-Panel Display with Dynamic Backlight Control Achieve higher image quality while reducing power and cost using Spartan-6 FPGAs with

Achieve higher image quality while reducing power and cost using Spartan-6 FPGAs with integrated serial I/O capabilities.

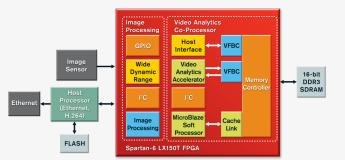

### Video Surveillance

Surveillance Image Capture and Analytics Engine

Integrate sensor interfacing, video analytics, image enhancement and network interfacing in a single Spartan-6 LX150T FPGA.

#### **Corporate Headquarters**

Xilinx, Inc. 2100 Logic Drive San Jose, CA 95124 USA Tel: 408-559-7778 www.xilinx.com

### Europe

Xilinx Europe One Logic Drive Citywest Business Campus Saggart, County Dublin Ireland Tel: +353-1-464-0311 www.xilinx.com

### Japan

Xilinx K.K. Art Village Osaki Central Tower 4F 1-2-2 Osaki, Shinagawa-ku Tokyo 141-0032 Japan Tel: +81-3-6744-7777 japan.xilinx.com

#### Asia Pacific Pte. Ltd.

Xilinx, Asia Pacific 5 Changi Business Park Singapore 486040 Tel: +65-6407-3000 www.xilinx.com

© Copyright 2011 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

#### Enhance the user experience

Spartan<sup>®</sup>-6 FPGAs provide the flexibility to respond rapidly to changing consumer requirements.

- Improve video performance with customized graphics accelerators and flexible parallel and serial interface capabilities

- Simplify interfacing to host processors and reduce component count with integrated PCI Express<sup>®</sup> technology

- Accelerate design with IP offerings for graphics processing, video conversion, high-speed interfacing, and vehicle networks

#### Increase picture quality

Spartan-6 FPGAs offer a cost-efficient alternative to ASICs and enable DTV manufacturers to rapidly develop and deliver displays offering a superior viewing experience within ever-shrinking product lifecycles.

- Achieve tough performance and EMI targets easily with low-jitter spread-spectrum clocking

- Reduce power consumption, simplify thermal management, increase reliability, and reduce cost with high-capacity, low-power FPGAs

- Increase image quality with a rich library of image enhancement IP such as dynamic gamma correction, motion adaptive temporal noise reduction, and dynamic range compression

- Simplify high-bandwidth interfaces with flexible SelectIO technology, an integrated memory controller block, and DisplayPort-enabled 3.2Gbps GTP transceivers

# Increase security through real-time image interpretation

Spartan-6 FPGAs offer the ideal combination of performance and flexibility to address requirements for high resolution, video analytics, and increased channels in video surveillance systems.

- Build flexible front-end image processing to support higher video resolutions

- Process native-resolution image data at full frame rate using highly parallel implementations based on DSP48A1 slices

- Implement edge-based video analytics with cost-effective customized co-processors